Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

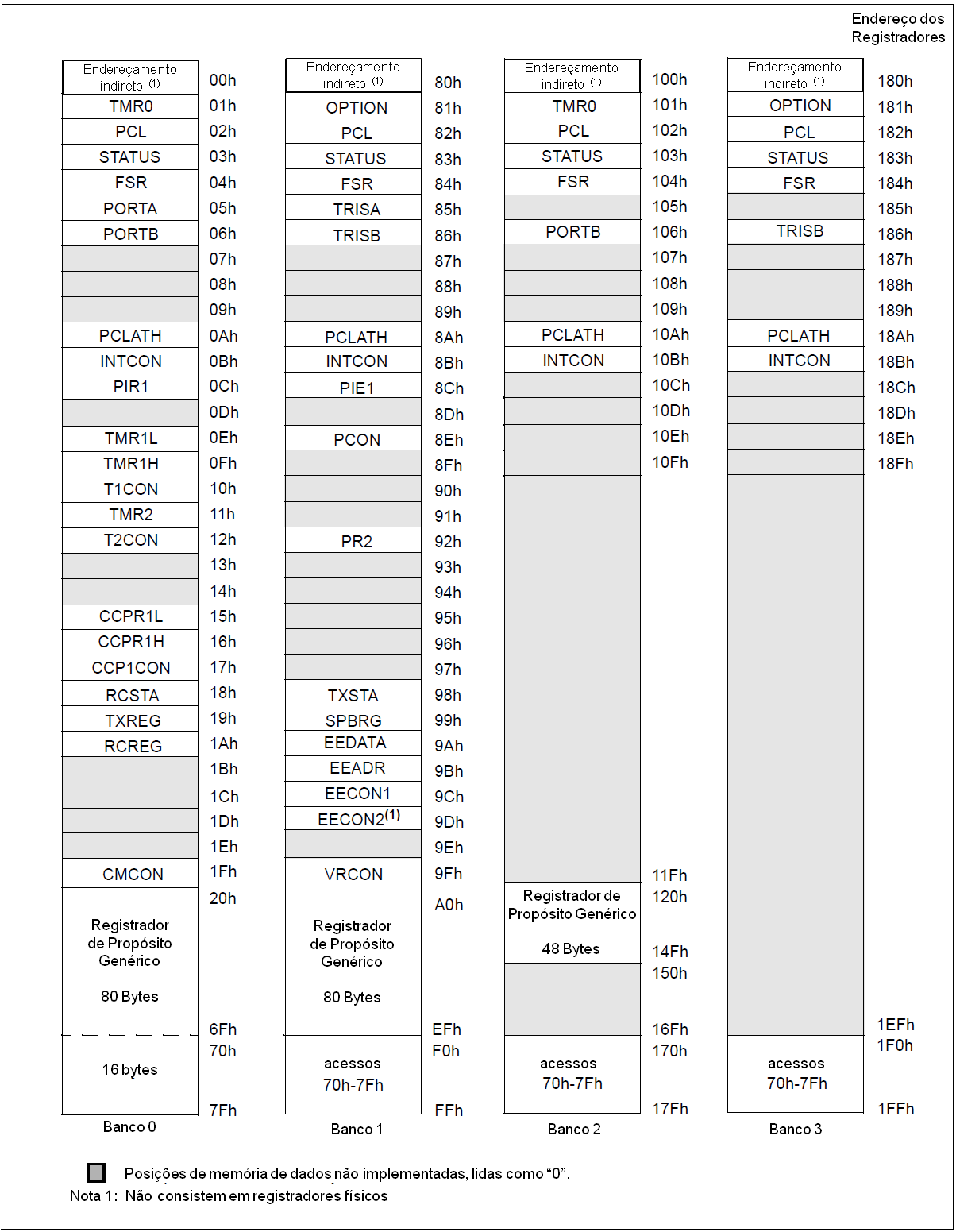

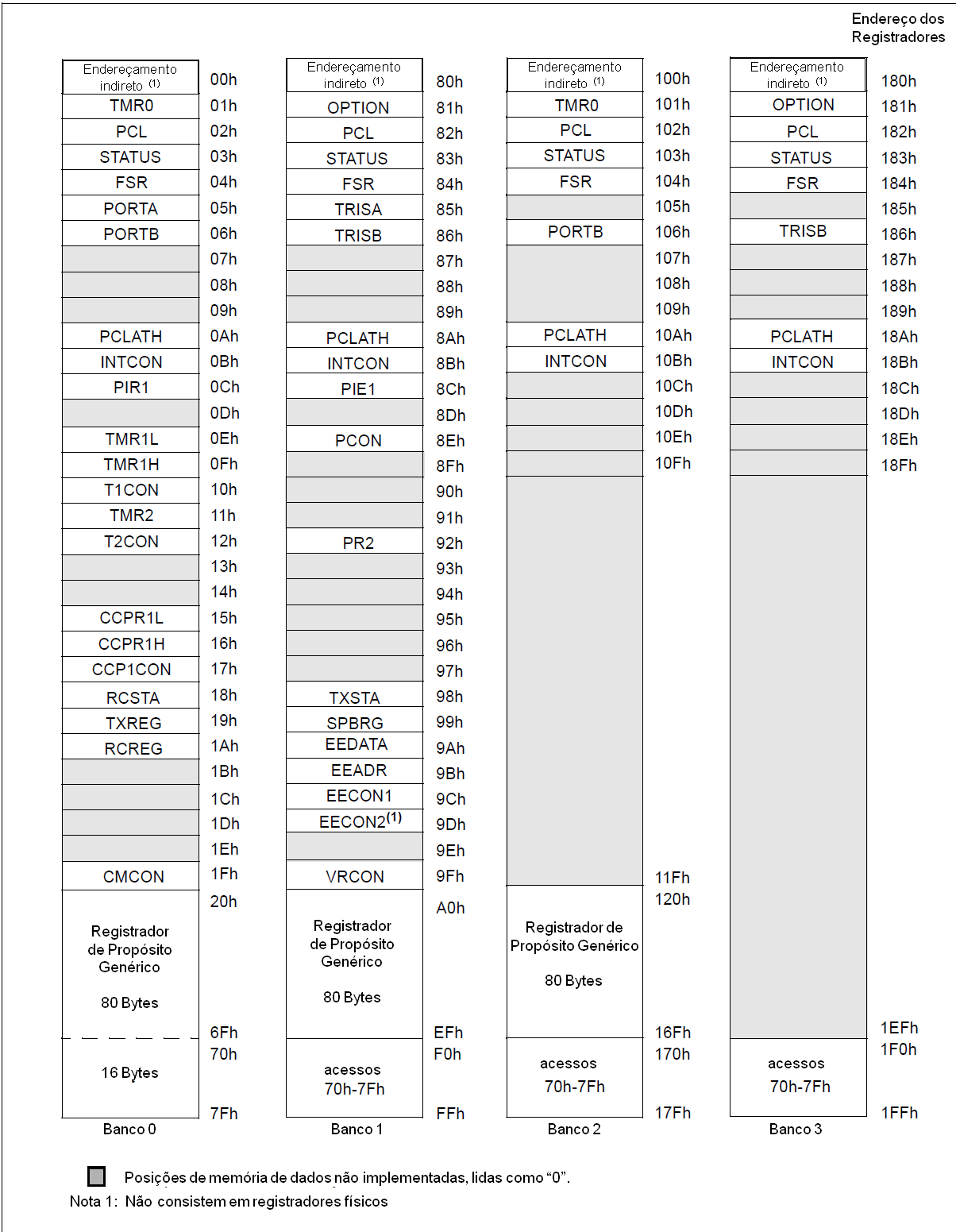

A memória de dados dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A (Figura 4.2 e Figura 4.3) é particionada em quatro bancos que contêm os Registradores de Propósitos Genéricos (General Purpose Registers - GPRs) e os Registradores de Funções Especiais (Special Function Registers - SFRs). Os SFRs estão localizados nas primeiras 32 posições de cada banco. Existem Registradores de Propósito Genérico implementados como RAM estática em cada banco. A Tabela 4.1 lista os Registradores de Propósito Genérico disponíveis em cada um dos quatro bancos.

Os endereços F0h-FFh, 170h-17Fh e 1F0h-1FFh são implementados como RAM comum e mapeados de volta aos endereços 70h-7Fh.

A Tabela 4.2 lista como acessar os quatro bancos de registradores através dos bits RP1 e RP0 do registrador de status.

|

Banco |

RP1 |

RP0 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

2 |

1 |

0 |

|

3 |

1 |

1 |

4.2.1 REGISTRADORES DE PROPÓSITO GENÉRICO

O banco de registradores é organizado em 224 x 8 nos PIC16F627A e PIC16F628A e em 256 x 8 no PIC16F648A. Cada um é acessado direta ou indiretamente pelo Registrador de Seleção de Memória (File Select Register - FSR), veja a Seção 4.4 "Endereçamento Indireto, Registradores INDF e FSR".

4.2.2 REGISTRADORES DE FUNÇÕES ESPECIAIS

Os SFRs são registradores utilizados pela CPU e pelas funções periféricas para controlar a operação desejada do dispositivo (Tabela 4.3). Estes registradores são uma RAM estática.

Os registradores especiais podem ser classificados em dois conjuntos (centrais e periféricos). Os SFRs associados a uma função central são descritos nesta seção. Aqueles relacionados à operação de disposivos periféricos são descritos na seção do respectivo dispositivo.

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR(1) |

Detalhes |

|

Banco 0 |

|

|

|

|

|

00h |

INDF |

O endereçamento desta posição utiliza o conteúdo do FSR para endereçar a memória de dados (não é um registrador físico) |

xxxx xxxx |

Detalhes |

|

01h |

TMR0 |

Registrador do Modulo Timer0 |

xxxx xxxx |

Detalhes |

|

02h |

PCL |

Byte Menos Significativo do Contador de Programa (PC) |

0000 0000 |

Detalhes |

|

03h |

STATUS |

IRP |

RP1 |

RP0 |

TO |

PD |

Z |

DC |

C |

0001 1xxx |

Detalhes |

|

04h |

FSR |

Apontador de Endereço da Memória de Dados Indiretos |

xxxx xxxx |

Detalhes |

|

05h |

PORTA |

RA7 |

RA6 |

RA5 |

RA4 |

RA3 |

RA2 |

RA1 |

RA0 |

xxxx 0000 |

Detalhes |

|

06h |

PORTB |

RB7 |

RB6 |

RB5 |

RB4 |

RB3 |

RB2 |

RB1 |

RB0 |

xxxx xxxx |

Detalhes |

|

07h |

--- |

Não implementado |

--- |

--- |

|

08h |

--- |

Não implementado |

--- |

--- |

|

09h |

--- |

Não implementado |

--- |

--- |

|

0Ah |

PCLATH |

--- |

--- |

--- |

Buffer de Escrita para os 5 bits superiores do Contador de Programa |

---0 0000 |

Detalhes |

|

0Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

Detalhes |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

Detalhes |

|

0Dh |

--- |

Não implementado |

--- |

--- |

|

0Eh |

TMR1L |

Holding Register para o Byte Menos Significativo do Registrador TMR1 de 16 bits |

xxxx xxxx |

Detalhes |

|

0Fh |

TMR1H |

Holding Register para o Byte Mais Significativo do Registrador TMR1 de 16 bits |

xxxx xxxx |

Detalhes |

|

10h |

T1CON |

--- |

--- |

T1CKPS1 |

T1CKPS0 |

T1OSCEN |

T1SYNC |

TMR1CS |

TMR1ON |

--00 0000 |

Detalhes |

|

11h |

TMR2 |

Registrador do Módulo TMR2 |

0000 0000 |

Detalhes |

|

12h |

T2CON |

--- |

TOUTPS3 |

TOUTPS2 |

TOUTPS1 |

TOUTPS0 |

TMR2ON |

T2CKPS1 |

T2CKPS0 |

-000 0000 |

Detalhes |

|

13h |

--- |

Não implementado |

--- |

--- |

|

14h |

--- |

Não implementado |

--- |

--- |

|

15h |

CCPR1L |

Registrador de Captura/ Comparação/ PWM (LSB) |

xxxx xxxx |

Detalhes |

|

16h |

CCPR1H |

Registrador de Captura/ Comparação/ PWM (MSB) |

xxxx xxxx |

Detalhes |

|

17h |

CCP1CON |

--- |

--- |

CCP1X |

CCP1Y |

CCP1M3 |

CCP1M2 |

CCP1M1 |

CCP1M0 |

--00 0000 |

Detalhes |

|

18h |

RCSTA |

SPEN |

RX9 |

SREN |

CREN |

ADEN |

FERR |

OERR |

RX9D |

0000 000x |

Detalhes |

|

19h |

TXREG |

Registrador de Dados Transmitidos do USART |

0000 0000 |

Detalhes |

|

1Ah |

RCREG |

Registrador de Dados Recebidos do USART |

0000 0000 |

Detalhes |

|

1Bh |

--- |

Não implementado |

--- |

--- |

|

1Ch |

--- |

Não implementado |

--- |

--- |

|

1Dh |

--- |

Não implementado |

--- |

--- |

|

1Eh |

--- |

Não implementado |

--- |

--- |

|

1Fh |

CMCON |

C2OUT |

C1OUT |

C2INV |

C1INV |

CIS |

CM2 |

CM1 |

CM0 |

0000 0000 |

Detalhes |

Legenda:

- = Posições não implementadas, lidas como '0'

u = inalterado

x = desconhecido

q = o valor depende da condição

células sombreadas = não implementado

Nota 1: Para a condição de inicialização para as tabelas de registradores, consulte as Tabelas 14.6 e 14.7.

TABELA 4.4: RESUMO DOS REGISTRADORES DE FUNÇÕES ESPECIAIS - BANCO 1

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR(1) |

Detalhes |

|

Banco 1 |

|

|

|

|

|

80h |

INDF |

O endereçamento desta posição utiliza o conteúdo do FSR para endereçar a memória de dados (não é um registrador físico) |

xxxx xxxx |

Detalhes |

|

81h |

OPTION |

RBPU |

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

1111 1111 |

Detalhes |

|

82h |

PCL |

Byte Menos Significativo do Contador de Programa (PC) |

0000 0000 |

Detalhes |

|

83h |

STATUS |

IRP |

RP1 |

RP0 |

TO |

PD |

Z |

DC |

C |

0001 1xxx |

Detalhes |

|

84h |

FSR |

Apontador de Endereço da Memória de Dados Indiretos |

xxxx xxxx |

Detalhes |

|

85h |

TRISA |

TRISA7 |

TRISA6 |

TRISA5 |

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

1111 1111 |

Detalhes |

|

86h |

TRISB |

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

1111 1111 |

Detalhes |

|

87h |

--- |

Não implementado |

--- |

--- |

|

88h |

--- |

Não implementado |

--- |

--- |

|

89h |

--- |

Não implementado |

--- |

--- |

|

8Ah |

PCLATH |

--- |

--- |

--- |

Buffer de Escrita para os 5 bits superiores do Contador de Programa |

---0 0000 |

Detalhes |

|

8Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

Detalhes |

|

8Ch |

PIE1 |

EEIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

Detalhes |

|

8Dh |

--- |

Não implementado |

--- |

--- |

|

8Eh |

PCON |

--- |

--- |

--- |

--- |

OSCF |

--- |

POR |

BOR |

---- 1-0x |

Detalhes |

|

8Fh |

--- |

Não Implementado |

--- |

--- |

|

90h |

--- |

Não Implementado |

--- |

--- |

|

91h |

--- |

Não Implementado |

--- |

--- |

|

92h |

PR2 |

Registrador de Período do Timer2 |

1111 1111 |

Detalhes |

|

93h |

--- |

Não implementado |

--- |

--- |

|

94h |

--- |

Não implementado |

--- |

--- |

|

95h |

--- |

Não implementado |

--- |

--- |

|

96h |

--- |

Não implementado |

--- |

--- |

|

97h |

--- |

Não implementado |

--- |

--- |

|

98h |

TXSTA |

CSRC |

TX9 |

TXEN |

SYNC |

--- |

BRGH |

TRMT |

TX9D |

0000 -010 |

Detalhes |

|

99h |

SPBRG |

Registrador Gerador da Taxa de Transmissão |

0000 0000 |

Detalhes |

|

9Ah |

EEDATA |

Registrador de Dados da EEPROM |

xxxx xxxx |

Detalhes |

|

9Bh |

EEADR |

Registrador de Endereço da EEPROM |

xxxx xxxx |

Detalhes |

|

9Ch |

EECON1 |

--- |

--- |

--- |

--- |

WRERR |

WREN |

WR |

RD |

---- x000 |

Detalhes |

|

9Dh |

EECON2 |

Registrador 2 de Controle da EEPROM (não é um registrador físico) |

---- ---- |

Detalhes |

|

9Eh |

--- |

Não implementado |

--- |

--- |

|

9Fh |

VRCON |

VREN |

VROE |

VRR |

--- |

VR3 |

VR2 |

VR1 |

VR0 |

000- 0000 |

Detalhes |

Legenda:

- = Posições não implementadas, lidas como '0'

u = inalterado

x = desconhecido

q = o valor depende da condição

células sombreadas = não implementado

Nota 1: Para a condição de inicialização para as tabelas de registradores, consulte as Tabelas 14.6 e 14.7.

TABELA 4.5: RESUMO DOS REGISTRADORES DE FUNÇÕES ESPECIAIS - BANCO 2

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR(1) |

Detalhes |

|

Banco 2 |

|

|

|

|

|

100h |

INDF |

O endereçamento desta posição utiliza o conteúdo do FSR para endereçar a memória de dados (não é um registrador físico) |

xxxx xxxx |

Detalhes |

|

101h |

TMR0 |

Registrador do Módulo do Timer0 |

xxxx xxxx |

Detalhes |

|

102h |

PCL |

Byte Menos Significativo do Contador de Programa (PC) |

0000 0000 |

Detalhes |

|

103h |

STATUS |

IRP |

RP1 |

RP0 |

TO |

PD |

Z |

DC |

C |

0001 1xxx |

Detalhes |

|

104h |

FSR |

Apontador de Endereço da Memória de Dados Indiretos |

xxxx xxxx |

Detalhes |

|

105h |

--- |

Não Implementado |

--- |

--- |

|

106h |

PORTB |

RB7 |

RB6 |

RB5 |

RB4 |

RB3 |

RB2 |

RB1 |

RB0 |

xxxx xxxx |

Detalhes |

|

107h |

--- |

Não implementado |

--- |

--- |

|

108h |

--- |

Não implementado |

--- |

--- |

|

109h |

--- |

Não implementado |

--- |

--- |

|

10Ah |

PCLATH |

--- |

--- |

--- |

Buffer de Escrita para os 5 bits superiores do Contador de Programa |

---0 0000 |

Detalhes |

|

10Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

Detalhes |

|

10Ch |

--- |

Não implementado |

--- |

--- |

|

10Dh |

--- |

Não implementado |

--- |

--- |

|

10Eh |

--- |

Não implementado |

--- |

--- |

|

10Fh |

--- |

Não Implementado |

--- |

--- |

|

110h |

--- |

Não Implementado |

--- |

--- |

|

111h |

--- |

Não Implementado |

--- |

--- |

|

112h |

--- |

Não implementado |

--- |

--- |

|

113h |

--- |

Não implementado |

--- |

--- |

|

114h |

--- |

Não implementado |

--- |

--- |

|

115h |

--- |

Não implementado |

--- |

--- |

|

116h |

--- |

Não implementado |

--- |

--- |

|

117h |

--- |

Não implementado |

--- |

--- |

|

118h |

--- |

Não implementado |

--- |

--- |

|

119h |

--- |

Não implementado |

--- |

--- |

|

11Ah |

--- |

Não implementado |

--- |

--- |

|

11Bh |

--- |

Não implementado |

--- |

--- |

|

11Ch |

--- |

Não implementado |

--- |

--- |

|

11Dh |

--- |

Não implementado |

--- |

--- |

|

11Eh |

--- |

Não implementado |

--- |

--- |

|

11Fh |

--- |

Não implementado |

--- |

--- |

Legenda:

- = Posições não implementadas, lidas como '0'

u = inalterado

x = desconhecido

q = o valor depende da condição

células sombreadas = não implementado

Nota 1: Para a condição de inicialização para as tabelas de registradores, consulte as Tabelas 14.6 e 14.7.

TABELA 4.6: RESUMO DOS REGISTRADORES DE FUNÇÕES ESPECIAIS - BANCO 3

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR(1) |

Detalhes |

|

Banco 3 |

|

|

|

|

|

180h |

INDF |

O endereçamento desta posição utiliza o conteúdo do FSR para endereçar a memória de dados (não é um registrador físico) |

xxxx xxxx |

Detalhes |

|

181h |

OPTION |

RBPU |

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

1111 1111 |

Detalhes |

|

182h |

PCL |

Byte Menos Significativo do Contador de Programa (PC) |

0000 0000 |

Detalhes |

|

183h |

STATUS |

IRP |

RP1 |

RP0 |

TO |

PD |

Z |

DC |

C |

0001 1xxx |

Detalhes |

|

184h |

FSR |

Apontador de Endereço da Memória de Dados Indiretos |

xxxx xxxx |

Detalhes |

|

185h |

--- |

Não Implementado |

--- |

--- |

|

186h |

TRISB |

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

1111 1111 |

Detalhes |

|

187h |

--- |

Não implementado |

--- |

--- |

|

188h |

--- |

Não implementado |

--- |

--- |

|

189h |

--- |

Não implementado |

--- |

--- |

|

18Ah |

PCLATH |

--- |

--- |

--- |

Buffer de Escrita para os 5 bits superiores do Contador de Programa |

---0 0000 |

Detalhes |

|

18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

Detalhes |

|

18Ch |

--- |

Não implementado |

--- |

--- |

|

18Dh |

--- |

Não implementado |

--- |

--- |

|

18Eh |

--- |

Não implementado |

--- |

--- |

|

18Fh |

--- |

Não Implementado |

--- |

--- |

|

190h |

--- |

Não Implementado |

--- |

--- |

|

191h |

--- |

Não Implementado |

--- |

--- |

|

192h |

--- |

Não implementado |

--- |

--- |

|

193h |

--- |

Não implementado |

--- |

--- |

|

194h |

--- |

Não implementado |

--- |

--- |

|

195h |

--- |

Não implementado |

--- |

--- |

|

196h |

--- |

Não implementado |

--- |

--- |

|

197h |

--- |

Não implementado |

--- |

--- |

|

198h |

--- |

Não implementado |

--- |

--- |

|

199h |

--- |

Não implementado |

--- |

--- |

|

19Ah |

--- |

Não implementado |

--- |

--- |

|

19Bh |

--- |

Não implementado |

--- |

--- |

|

19Ch |

--- |

Não implementado |

--- |

--- |

|

19Dh |

--- |

Não implementado |

--- |

--- |

|

19Eh |

--- |

Não implementado |

--- |

--- |

|

19Fh |

--- |

Não implementado |

--- |

--- |

Legenda:

- = Posições não implementadas, lidas como '0'

u = inalterado

x = desconhecido

q = o valor depende da condição

células sombreadas = não implementado

Nota 1: Para a condição de inicialização para as tabelas de registradores, consulte as Tabelas 14.6 e 14.7.

Este tópico divide-se para detalhar os seguintes registradores: