Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

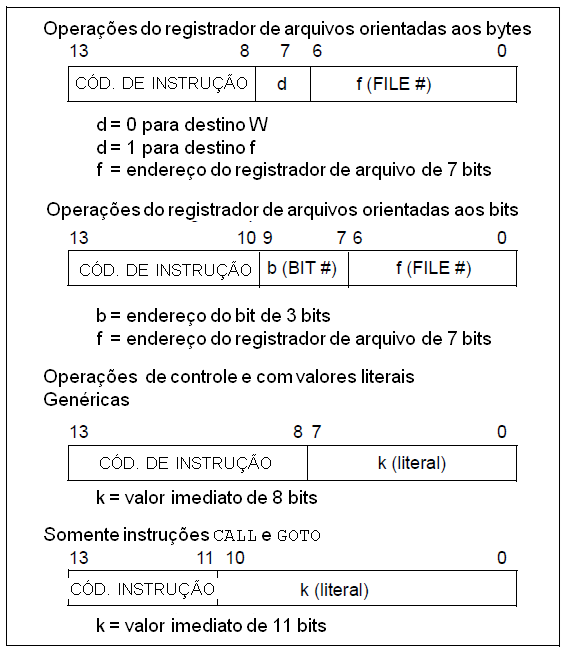

Cada instrução dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A é uma palavra de 14 bits dividida entre um código de instrução (OPCODE) que especifica o tipo de instrução e um ou mais operandos que especificam a operação da instrução. O resumo do conjunto de instruções dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A na Tabela 15.2 lista as operações orientadas a bytes, orientadas a bits e de controle com valores literais. A Tabela 15.1 apresenta as descrições do campo do código de instrução.

Para instruções orientadas a bytes, 'f' representa um designador de registrador de memória e 'd' representa um designador de destino. O designador de registrador de memória especifica qual registrador de memória será usado pela instrução.

O designador de destino especifica onde o resultado da operação será colocado. Se 'd' for zero, o resultado é colocado no registrador W, Se 'd' for um, o resultado é colocado no registrador de memória especificado na instrução.

Para instruções orientadas a bits, 'b' representa um designador de campo de bit, o qual seleciona o número do bit afetado pela operação, enquanto 'f' representa o número do registrador de memória no qual o bit é colocado.

Para operações de controle e com valores literais, 'k' representa uma constante ou valor literal de oito ou onze bits.

15.1 Operações Ler-Modificar-Escrever

Qualquer instrução que especifique um registrador de memória como parte da instrução resulta em uma operação do tipo Ler-Modificar-Escrever (Read-Modify-Write, R-M-W). O registrador é lido, os dados são modificados e o resultado é armazenado de acordo com a instrução ou com o designador de destino 'd'. Uma operação de leitura é executada em um registrador mesmo que a instrução execute uma escrita naquele registrador.

Por exemplo, uma instrução "clrf PORTB" executará uma leitura na PORTB, apagará todos os bits de dados, e então escreverá o resultado novamente na PORTB. Este exemplo teria o resultado não intencional de que a condição que ativa o sinalizador RBIF seria apagada para pinos que estiverem configurados como entrada e utilizando a propriedade interrupt-on-change da PORTB.

|

Campo |

Descrição |

|

f |

Endereço do registrador de memória (0x00 até 0x7F) |

|

W |

Registrador de trabalho (acumulador) |

|

b |

Endereço do bit em um registrador de memória de 8 bits |

|

k |

Campo literal, dados constantes ou label |

|

x |

Posição "indiferente" ("don't care"); = 0 ou 1

O assembler gerará o código com x = 0. É a forma de utilização recomendada para compatibilidade com todas as ferramentas de software da Microchip. |

|

d |

Seleção do destino;

d = 0: armazena o resultado em W,

d = 1: armazena o resultado no registrador do arquivo f.

O padrão é d = 1. |

|

TO |

Bit de esgotamento de tempo (time-out) |

|

PD |

Bit de desligamento (power-down) |

O conjunto de instruções é estritamente ortogonal e é agrupado em três categorias básicas:

-

Operações orientadas aos bytes

-

Operações orientadas aos bits

-

Operações de controle e com valores literais

Todas as instruções são executadas em um único ciclo de instrução, a menos que um teste condicional resulte em verdadeiro ou que o contador do programa seja alterado como o resultado de uma instrução. Neste caso, a execução levará dois ciclos, sendo o segundo ciclo executado como um NOP. Um ciclo de instrução consiste em quatro períodos de oscilador. Portanto, para uma frequência de oscilador de 4 MHz, o tempo normal de execução da instrução é 1μs. Se um teste condicional resulta em verdadeiro ou se o contador do programa é alterado como resultado de uma instrução, o tempo de execução da instrução é 2μs.

A Tabela 15.2 lista as instruções reconhecidas pelo assembler MPASM™.

A Figura 15.1 apresenta os três formatos genéricos que as instruções podem ter.

Nota 1: Qualquer código de instrução não-utilizado é reservado. A utilização de qualquer código de instrução reservado pode causar uma operação não esperada.

Nota 2: Para manter uma compatibilidade constante com os futuros produtos PIC MCU, não utilize as instruções OPTION e TRIS.

Todos os exemplos utilizam o seguinte formato para representar um número hexadecimal:

0xhh

onde 'h' significa um dígito hexadecimal.

|

Mnemônico, Operandos |

Descrição |

Ciclos |

Código de Instrução de 14 Bits |

Bits de Status Afetados |

Notas |

|

MSb |

|

|

LSb |

OPERAÇÕES ORIENTADAS AOS BYTES DO REGISTRADOR DE MEMÓRIA |

|

ADDWF |

f,d |

Soma os valores de W e f |

1 |

00 |

0111 |

dfff |

ffff |

C, DC, Z |

1, 2 |

|

ANDWF |

f,d |

Realiza a operação lógica "E" entre os valores de W e f |

1 |

00 |

0101 |

dfff |

ffff |

Z |

1, 2 |

|

CLRF |

f |

Apaga f |

1 |

00 |

0001 |

1fff |

ffff |

Z |

2 |

|

CLRW |

--- |

Apaga W |

1 |

00 |

0001 |

0xxx |

xxxx |

Z |

|

|

COMF |

f,d |

Complementa o valor de f |

1 |

00 |

1001 |

dfff |

ffff |

Z |

1, 2 |

|

DECF |

f,d |

Diminui uma unidade do valor de f |

1 |

00 |

0011 |

dfff |

ffff |

Z |

1, 2 |

|

DECFSZ |

f,d |

Diminui uma unidade do valor de f, pula a instrução seguinte se o resultado for 0 |

1(2) |

00 |

1011 |

dfff |

ffff |

|

1, 2, 3 |

|

INCF |

f,d |

Aumenta uma unidade do valor de f |

1 |

00 |

1010 |

dfff |

ffff |

Z |

1, 2 |

|

INCFSZ |

f,d |

Aumenta uma unidade do valor de f, pula a instrução seguinte se o resultado for 0 |

1(2) |

00 |

1111 |

dfff |

ffff |

|

1, 2, 3 |

|

IORWF |

f,d |

Realiza a operação lógica "OU" entre os valores de W e f |

1 |

00 |

0100 |

dfff |

ffff |

Z |

1, 2 |

|

MOVF |

f,d |

Move o valor de f |

1 |

00 |

1000 |

dfff |

ffff |

Z |

1, 2 |

|

MOVWF |

f |

Move o valor de W para f |

1 |

00 |

0000 |

1fff |

ffff |

|

|

|

NOP |

--- |

Nenhuma operação |

1 |

00 |

0000 |

0xx0 |

0000 |

|

|

|

RLF |

f,d |

Rotaciona o valor de f para a esquerda através do bit Carry |

1 |

00 |

1101 |

dfff |

ffff |

C |

1, 2 |

|

RRF |

f,d |

Rotaciona o valor de f para a direita através do bit Carry |

1 |

00 |

1100 |

dfff |

ffff |

C |

1, 2 |

|

SUBWF |

f,d |

Subtrai o valor de W do valor de f |

1 |

00 |

0010 |

dfff |

ffff |

C, DC, Z |

1, 2 |

|

SWAPF |

f,d |

Troca os nibbles em f |

1 |

00 |

1110 |

dfff |

ffff |

|

1, 2 |

|

XORWF |

f,d |

Realiza a operação lógica "OU EXCLUSIVO" entre os valores de W e f |

1 |

00 |

0110 |

dfff |

ffff |

Z |

1, 2 |

OPERAÇÕES ORIENTADAS AOS BITS DO REGISTRADOR DE MEMÓRIA |

|

BCF |

f,b |

Apaga o bit de f |

1 |

01 |

00bb |

bfff |

ffff |

|

1, 2 |

|

BSF |

f,b |

Ativa o bit de f |

1 |

01 |

01bb |

bfff |

ffff |

|

1, 2 |

|

BTFSC |

f,b |

Testa o bit de f, pula a instrução seguinte se o bit estiver apagado |

1(2) |

01 |

10bb |

bfff |

ffff |

|

3 |

|

BTFSS |

f,b |

Testa o bit de f, pula a instrução seguinte se o bit estiver ativado |

1(2) |

01 |

11bb |

bfff |

ffff |

|

3 |

OPERAÇÕES DE CONTROLE E COM VALORES LITERAIS |

|

ADDLW |

k |

Soma o valor literal com o valor de W |

1 |

11 |

111x |

kkkk |

kkkk |

C, DC, Z |

|

|

ANDLW |

k |

Realiza a operação lógica "E" entre o valor literal e o valor de W |

1 |

11 |

1001 |

kkkk |

kkkk |

Z |

|

|

CALL |

k |

Chama a subrotina |

2 |

10 |

0kkk |

kkkk |

kkkk |

|

|

|

CLRWDT |

--- |

Apaga o Temporizador Cão-de-Guarda |

1 |

00 |

0000 |

0110 |

0100 |

TO, PD |

|

|

GOTO |

k |

Vai para o endereço |

2 |

10 |

1kkk |

kkkk |

kkkk |

|

|

|

IORLW |

k |

Realiza a operação lógica "OU" entre o valor literal e o valor de W |

1 |

11 |

1000 |

kkkk |

kkkk |

Z |

|

|

MOVLW |

k |

Move o valor literal para W |

1 |

11 |

00xx |

kkkk |

kkkk |

|

|

|

RETFIE |

--- |

Retorna da interrupção |

2 |

00 |

0000 |

0000 |

1001 |

|

|

|

RETLW |

k |

Retorna com o valor literal em W |

2 |

11 |

01xx |

kkkk |

kkkk |

|

|

|

RETURN |

--- |

Retorna da subrotina |

2 |

00 |

0000 |

0000 |

1000 |

|

|

|

SLEEP |

--- |

Vai para o modo de Hibernação |

1 |

00 |

0000 |

0110 |

0011 |

TO, PD |

|

|

SUBLW |

k |

Subtrai o valor de W do valor literal |

1 |

11 |

110x |

kkkk |

kkkk |

C, DC, Z |

|

|

XORLW |

k |

Realiza a operação lógica "OU EXCLUSIVO" entre o valor literal e o valor de W |

1 |

11 |

1010 |

kkkk |

kkkk |

Z |

|

Notas:

1: Quando um registrador de I/O for modificado em função dele mesmo (p. ex. MOVF PORTB, 1), o valor utilizado será aquele presente nos próprios pinos. Por exemplo, se a latch de dados for '1' para um pino configurado como entrada e for levada para baixo por um dispositivo externo, os dados serão escritos de volta com um '0'.

2: Se esta instrução for executada no registrador TMR0 (e, quando aplicável, d = 1), o prescaler será apagado se designado para o módulo Timer0.

3: Se o Contador do Programa (PC) for modificado ou um teste condicional for verdadeiro, a instrução requer dois ciclos. O segundo ciclo é executado como uma NOP.

15.2 Descrição das Instruções

|

ADDLW |

Soma o Valor Literal com o Valor de W |

|

Sintaxe: |

[rótulo] ADDLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

|

Operação: |

(W) + k → (W) |

|

Bits de Status Afetados: |

C, DC, Z |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador W é adicionado ao valor literal 'k' de oito bits e o resultado é colocado no registrador W. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

ADDLW 0x15

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

ADDWF |

Soma os Valores de W e f |

|

Sintaxe: |

[rótulo] ADDWF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(W) + (f) → (dest) |

|

Bits de Status Afetados: |

C, DC, Z |

|

Codificação: |

|

|

Descrição: |

Adiciona o conteúdo do registrador W com o registrador 'f'. Se 'd' for '0', o resultado é armazenado no registrador W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

ADDWF REG1, 0

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

W = 0xD9

REG1 = 0xC2

Z = 0

C = 0

DC = 0 |

|

|

ANDLW |

Realiza a Operação Lógica "E" entre o Valor Literal e o Valor de W |

|

Sintaxe: |

[rótulo] ANDLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

|

Operação: |

(W) .AND. (k) → (W) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

Uma operação 'E' lógica é executada entre o conteúdo do registrador W e o valor literal 'k' de oito bits. O resultado é colocado no registrador W. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

ANDLW 0x5F

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

ANDWF |

Realiza a Operação Lógica "E" entre os Valores de W e f |

|

Sintaxe: |

[rótulo] ANDWF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(W) .AND. (f) → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

Uma operação 'E' lógica é executada entre o registrador W e o registrador 'f'. Se 'd' for '0', o resultado é armazenado no registrador W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

ANDWF REG1, 1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

BCF |

Apaga o Bit de f |

|

Sintaxe: |

[rótulo] BCF f,b |

Operandos:

|

0 ≤ f ≤ 127

0 ≤ b ≤ 7 |

|

Operação: |

0 → (f<b>) |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O bit 'b' no registrador 'f' é apagado. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

BCF REG1, 7

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

BSF |

Ativa o Bit de f |

|

Sintaxe: |

[rótulo] BSF f,b |

Operandos:

|

0 ≤ f ≤ 127

0 ≤ b ≤ 7 |

|

Operação: |

1 → (f<b>) |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O bit 'b' no registrador 'f' é ativado. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

BSF REG1, 7

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

BTFSC |

Testa o Bit de f, Pula a Instrução Seguinte se o Bit Estiver Apagado |

|

Sintaxe: |

[rótulo] BTFSC f,b |

Operandos:

|

0 ≤ f ≤ 127

0 ≤ b ≤ 7 |

|

Operação: |

pula se (f<b>) = 0 |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Se o bit 'b' no registrador 'f' for '0', então a próxima instrução é pulada. Se o bit 'b' for '0', então a próxima instrução acessada durante a execução da instrução atual é descartada, e uma NOP é executada ao invés dela, fazendo desta uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

1(2) |

Exemplo

|

HERE BTFSC REG1

FALSE GOTO PROCESS_CODE

TRUE .

.

.

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

se REG<1> = 0,

PC = endereço TRUE

se REG<1> = 1,

PC = endereço FALSE |

|

|

BTFSS |

Testa o Bit de f, Pula a Instrução Seguinte se o Bit Estiver Ativado |

|

Sintaxe: |

[rótulo] BTFSS f,b |

Operandos:

|

0 ≤ f ≤ 127

0 ≤ b < 7 |

|

Operação: |

pula se (f<b>) = 1 |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Se o bit 'b' no registrador 'f' for '1', então a próxima instrução é pulada. Se o bit 'b' for '1', então a próxima instrução acessada durante a execução da instrução atual é descartada, e uma NOP é executada ao invés dela, fazendo desta uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

1(2) |

Exemplo

|

HERE BTFSS REG1

FALSE GOTO PROCESS_CODE

TRUE .

.

.

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

se FLAG<1> = 0,

PC = endereço FALSE

se FLAG<1> = 1,

PC = endereço TRUE |

|

|

CALL |

Chama a Subrotina |

|

Sintaxe: |

[rótulo] CALL k |

|

Operandos: |

0 ≤ k ≤ 2047 |

Operação:

|

(PC) + 1 → TOS,

k → PC<10:0>,

(PCLATH<4:3>) → PC<12:11> |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Chama a subrotina. Primeiramente, o endereço de retorno (PC + 1) é colocado na pilha. O endereço imediato do bit onze é carregado nos bits <10:0> do PC. Os bits mais altos do PC são carregados a partir do PCLATH. A CALL é uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

2 |

|

Exemplo |

HERE CALL THERE

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

PC = endereço THERE

TOS = endereço THERE + 1 |

|

|

CLRF |

Apaga f |

|

Sintaxe: |

[rótulo] CLRF f |

|

Operandos: |

0 ≤ f ≤ 127 |

Operação:

|

00h → (f)

1 → Z |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é apagado e o bit Z é ativado. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

CLRF REG1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

CLRW |

Apaga W |

|

Sintaxe: |

[rótulo] CLRW |

|

Operandos: |

Nenhum |

Operação:

|

00h → (W)

1 → Z |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

O registrador W é apagado. O bit zero (Z) é ativado. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

CLRW

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

CLRWDT |

Apaga o Temporizador Cão-de-Guarda |

|

Sintaxe: |

[rótulo] CLRWDT |

|

Operandos: |

Nenhum |

Operação:

|

00h → WDT

0 → pré-scaler de W

1 → TO

1 → PD |

|

Bits de Status Afetados: |

TO, PD |

|

Codificação: |

|

|

Descrição: |

A instrução CLRWDT reinicializa o Temporizador Cão-de-Guarda. Ela também reinicializa o pré-scaler do WDT. Os bits de status TO e PD são ativados. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

CLRWDT

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

contador do WDT = 0x00

pré-scaler do WDT = 0

TO = 1

PD = 1 |

|

|

COMF |

Complementa o valor de f |

|

Sintaxe: |

[rótulo] COMF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é complementado. Se 'd' for '0', o resultado é armazenado em W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

COMF REG1, 0

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

DECF |

Diminui uma Unidade do Valor de f |

|

Sintaxe: |

[rótulo] DECF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) - 1 → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

Decrementa uma unidade do valor do registrador 'f'. Se 'd' for '0', o resultado é armazenado no registrador W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

DECF CNT, 1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

DECFSZ |

Diminui uma Unidade do Valor de f, Pula a Instrução Seguinte se o Resultado for 0 |

|

Sintaxe: |

[rótulo] DECFSZ f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) - 1 → (dest); pula se resultado = 0 |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é decrementado em uma unidade. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é colocado de volta no registrador 'f'. Se o resultado for '0', a próxima instrução, que já está acessada, é descartada. Uma NOP é executada ao invés dela, fazendo desta uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

1(2) |

Exemplo

|

HERE DECFSZ REG1, 1

GOTO LOOP

CONTINUE .

.

.

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = REG1 - 1

se REG1 = 0,

PC = endereço CONTINUE

se REG1 ≠ 0,

PC = endereço HERE + 1 |

|

|

GOTO |

Desvio Incondicional |

|

Sintaxe: |

[rótulo] GOTO k |

|

Operandos: |

0 ≤ k ≤ 2047 |

Operação:

|

k → PC<10:0>

PCLATH<4:3> → PC<12:11> |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

A instrução GOTO é um desvio incondicional. O valor imediato do décimo primeiro bit é carregado para os bits do PC <10:0>. Os bits superiores do PC são carregados a partir do PCLATH<4:3>. A GOTO é uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

2 |

|

Exemplo |

GOTO THERE

|

|

|

Depois da Instrução |

|

|

|

|

INCF |

Aumenta uma Unidade do Valor de f |

|

Sintaxe: |

[rótulo] INCF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) + 1 → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é incrementado de uma unidade. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é colocado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

INCF REG1, 1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

INCFSZ |

Aumenta uma Unidade do Valor de f, Pula a Instrução Seguinte se o Resultado for 0 |

|

Sintaxe: |

[rótulo] INCFSZ f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) + 1 → (dest), pula se resultado = 0 |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é incrementado de uma unidade. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é colocado de volta no registrador 'f'. Se o resultado for '0', a próxima instrução, que já está acessada, é descartada. Uma instrução NOP é executada ao invés dela, fazendo desta uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

1(2) |

Exemplo

|

HERE INCFSZ REG1, 1

GOTO LOOP

CONTINUE .

.

.

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = REG1 + 1

se CNT = 0,

PC = endereço CONTINUE

se REG1 ≠ 0,

PC = endereço HERE + 1 |

|

|

IORLW |

Realiza a Operação Lógica "OU" entre o Valor Literal e o Valor de W |

|

Sintaxe: |

[rótulo] IORLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

|

Operação: |

(W) .OR. k → (W) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

É realizada a operação lógica "OU" entre o conteúdo do registrador W e o valor literal 'k' de oito bits. O resultado é colocado no registrador W. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

IORLW 0x35

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

IORWF |

Realiza a Operação Lógica "OU" entre os Valores de W e f |

|

Sintaxe: |

[rótulo] IORWF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(W) .OR. (f) → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

É realizada a operação lógica "OU" entre o registrador W e o registrador 'f'. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é colocado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

IORWF REG1, 0

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = 0x13

W = 0x93

Z = 1 |

|

|

MOVLW |

Move o Valor Literal para W |

|

Sintaxe: |

[rótulo] MOVLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

|

Operação: |

k → (W) |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O valor literal 'k' de oito bits é carregado para o registrador W. Os bits "indiferentes" (don´t care's) serão montados como '0's pelo assembler |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

MOVLW 0x5A

|

|

|

Depois da Instrução |

|

|

|

|

MOVF |

Move o Valor de f |

|

Sintaxe: |

[rótulo] MOVF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é movido para um destino que depende do status de 'd'. Se d = 0, o destino é o registrador W. Se d = 1, o destino é o próprio registrador de memória f. d = 1 é útil para se testar um registrador de memória, tendo em vista que o sinalizador de status Z é afetado. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

MOVF REG1, 0

|

|

|

Depois da Instrução |

|

|

|

|

W = valor no registrador REG1

Z = 1 |

|

|

MOVWF |

Move o Valor de W para f |

|

Sintaxe: |

[rótulo] MOVWF f |

|

Operandos: |

0 ≤ f ≤ 127 |

|

Operação: |

(W) → (f) |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Move os dados do registrador W para o registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

MOVWF REG1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

NOP |

Nenhuma Operação |

|

Sintaxe: |

[rótulo] NOP |

|

Operandos: |

Nenhum |

|

Operação: |

Nenhuma operação |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Nenhuma operação. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

NOP

|

|

OPTION |

Carrega o Registrador de Opção |

|

Sintaxe: |

[rótulo] OPTION |

|

Operandos: |

Nenhum |

|

Operação: |

(W) → OPTION |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador W é carregado no registrador OPTION (registrador de opção), Esta instrução é suportada por compatibilidade de código com os produtos PIC16C5X. Como o OPTION é um registrador de leitura e escrita, o usuário pode endereçá-lo diretamente utilizando somente uma instrução de registrador tal como MOVWF. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

|

|

|

Para manter uma compatibilidade constante com os futuros produtos PIC® MCU, não utilize esta instrução. |

|

RETFIE |

Retorna da Interrupção |

|

Sintaxe: |

[rótulo] RETFIE |

|

Operandos: |

Nenhum |

Operação:

|

TOS → PC,

1 → GIE |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Retorna da interrupção. A pilha é descarregada (POPed) e o topo da mesma (TOS = Top-of-Stack) é carregado no PC. Interrupções são habilitadas ativando-se o bit de Habilitação de Interrupção Global (Global Interrupt Enable), GIE (INTCON<7>). Esta é uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

2 |

|

Exemplo |

RETFIE

|

|

|

Depois da Interrupção |

|

|

|

|

RETLW |

Retorna com Valor Literal em W |

|

Sintaxe: |

[rótulo] RETLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

Operação:

|

k → (W);

TOS → PC |

|

Bits de Status Afetado: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

O registrador W é carregado com o valor literal 'k' de oito bits. O contador do programa é carregado a partir do topo da pilha (o endereço de retorno). Esta é uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

2 |

Exemplo

|

CALL TABLE ;W contém o valor

;do offset da tabela

. ;W possui agora o valor da tabela

.

.

TABLE

ADDWF PC ;W = offset

RETLW k1 ;Inicio da tabela

RETLW k2 ;

.

.

.

RETLW kn ;Fim da tabela

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

RETURN |

Retorna da Subrotina |

|

Sintaxe: |

[rótulo] RETURN |

|

Operandos: |

Nenhum |

|

Operação: |

TOS → PC |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Retorna da subrotina. A pilha é é descarregada (POPed) e o topo da mesma (TOS = top of the stack) é carregado para o contador do programa PC. Esta é uma instrução de dois ciclos. |

|

Palavras: |

1 |

|

Ciclos: |

2 |

|

Exemplo |

RETURN

|

|

|

Depois da Interrupção |

|

|

|

|

RLF |

Rotaciona o Valor de f para a Esquerda através do Bit Carry |

|

Sintaxe: |

[rótulo] RLF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

Veja descrição abaixo |

|

Bits de Status Afetados: |

C |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é rotacionado para a esquerda em um bit, através do Sinalizador Carry. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

|

|

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

RLF REG1, 0

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = 1110 0110

W = 1100 1100

C = 1 |

|

|

RRF |

Rotaciona o Valor de f para a Direita através do Bit Carry |

|

Sintaxe: |

[rótulo] RRF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

Veja descrição abaixo |

|

Bits de Status Afetados: |

C |

|

Codificação: |

|

|

Descrição: |

O conteúdo do registrador 'f' é rotacionado para a direita em um bit, através do Sinalizador Carry. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é colocado de volta no registrador 'f'. |

|

|

|

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

RRF REG1, 0

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = 1110 0110

W = 0111 0011

C = 0 |

|

|

SLEEP |

|

|

Sintaxe: |

[rótulo] SLEEP |

|

Operandos: |

Nenhum |

Operação:

|

00h → WDT,

0 → pré-scaler do WDT

1 → TO,

0 → PD |

|

Bits de Status Afetados: |

TO, PD |

|

Codificação: |

|

|

Descrição: |

O bit de Status de desativação, PD, é apagado. O bit de Status de esgotamento de tempo, TO, é ativado. O Temporizador Cão-de-Guarda e o seu pré-scaler são apagados. O processador é colocado no modo de Hibernação, com o oscilador parado. Veja a Seção 14.8 "Modo de Desativação (Hibernação)" para mais detalhes |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

SLEEP

|

|

SUBLW |

Subtrai o Valor de W do Valor Literal |

|

Sintaxe: |

[rótulo] SUBLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

|

Operação: |

k - (W) → (W) |

|

Bits de Status Afetados: |

C, DC, Z |

|

Codificação: |

|

|

Descrição: |

O valor do registrador W é subtraído (método do complemento dos 2's) do valor literal 'k' de oito bits. O resultado é colocado no registrador W. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo 1: |

SUBLW 0x02

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

W = 1

C = 1; resultado é positivo |

|

|

Exemplo 2: |

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

W = 0

C = 1; resultado é zero |

|

|

Exemplo 3: |

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

W = 0xFF

C = 0; resultado é negativo |

|

|

SUBWF |

Subtrai o Valor de W do Valor de f |

|

Sintaxe: |

[rótulo] SUBWF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(f) - (W) → (dest) |

|

Bits de Status Afetados: |

C, DC, Z |

|

Codificação: |

|

|

Descrição: |

Subtrai (método do complemento dos 2's) o valor do registrador W do valor do registrador 'f'. Se 'd' for '0', o resultado é armazenado no registrador W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo 1: |

SUBWF REG1, 1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = 1

W = 2

C = 1; resultado é positivo

DC = 1

Z = 0 |

|

|

Exemplo 2: |

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = 0

W = 2

C = 1; resultado é zero

Z = DC = 1 |

|

|

Exemplo 3: |

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

REG1 = 0xFF

W = 2

C = 0; resultado é negativo

Z = DC = 0 |

|

|

SWAPF |

Troca os Nibbles em f |

|

Sintaxe: |

[rótulo] SWAPF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

Operação:

|

(f<3:0>) → (dest<7:4>),

(f<7:4>) → (dest<3:0>) |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

Os nibbles superiores e inferiores do registrador 'f' são trocados entre si. Se 'd' for '0', o resultado é colocado no registrador W. Se 'd' for '1', o resultado é colocado no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

SWAPF REG1, 0

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

TRIS |

Carrega o Registrador TRIS |

|

Sintaxe: |

[rótulo] TRIS f |

|

Operandos: |

5 ≤ f ≤ 7 |

|

Operação: |

(W) → registrador 'f' TRIS; |

|

Bits de Status Afetados: |

Nenhum |

|

Codificação: |

|

|

Descrição: |

A instrução é suportada por compatibilidade de código com os produtos PIC16C5X. Como os registradores TRIS são de leitura e de escrita, o usuário pode endereçá-los diretamente. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

|

|

|

Para manter uma compatibilidade constante com os futuros produtos PIC® MCU, não utilize esta instrução. |

|

XORLW |

Realiza a Operação Lógica "OU EXCLUSIVO" entre o Valor Literal e o Valor de W |

|

Sintaxe: |

[rótulo] XORLW k |

|

Operandos: |

0 ≤ k ≤ 255 |

|

Operação: |

(W) .XOR. k → (W) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

É realizada a operação lógica "OU EXCLUSIVO" entre o conteúdo do registrador W e o valor literal 'k' de oito bits. O resultado é colocado no registrador W. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

XORLW 0xAF

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|

|

XORWF |

Realiza a Operação Lógica "OU EXCLUSIVO" entre os Valores de W e f |

|

Sintaxe: |

[rótulo] XORWF f,d |

Operandos:

|

0 ≤ f ≤ 127

d ∈ [0,1] |

|

Operação: |

(W) .XOR. (f) → (dest) |

|

Bits de Status Afetados: |

Z |

|

Codificação: |

|

|

Descrição: |

É realizada a operação lógica "OU EXCLUSIVO" entre o conteúdo do registrador W e o registrador 'f'. Se 'd' for '0', o resultado é armazenado no registrador W. Se 'd' for '1', o resultado é armazenado de volta no registrador 'f'. |

|

Palavras: |

1 |

|

Ciclos: |

1 |

|

Exemplo |

XORWF REG1, 1

|

|

|

Antes da Instrução |

|

|

|

|

|

Depois da Instrução |

|

|

|