Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

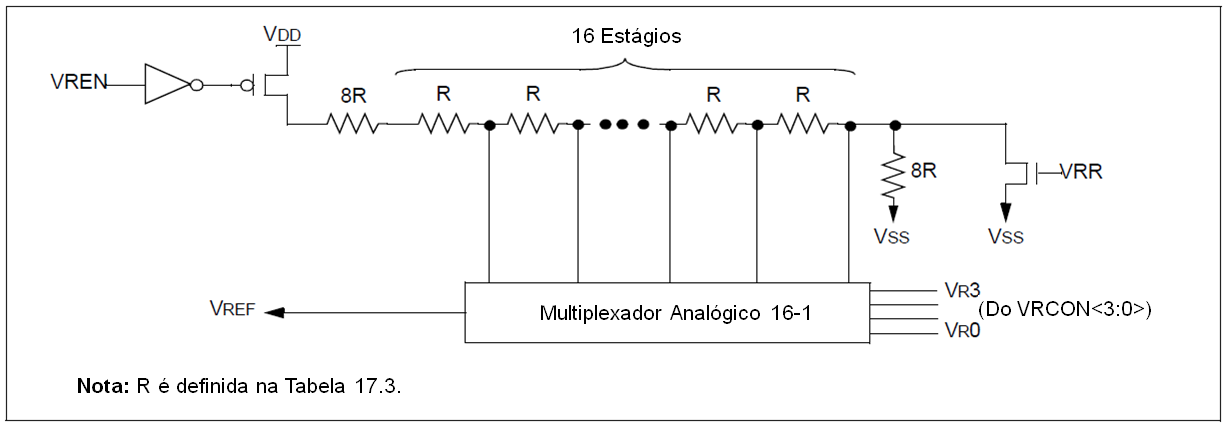

O módulo de Referência de Tensão dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A consiste em uma rede de resistores em escada com 16 degraus, a qual provê uma referência de tensão selecionável. A escada de resistores é segmentada a fim de fornecer dois intervalos de valores da VREF e possui uma função de desativação para economizar energia quando a referência não está sendo utilizada. O registrador VRCON controla a operação da referência, como apresentado na Figura 11.1. O diagrama de blocos é mostrado na Figura 11.1.

11.1 Configuração da Referência de Tensão

O módulo de Referência de Tensão pode ter como saída 16 diferentes níveis de tensão para cada intervalo.

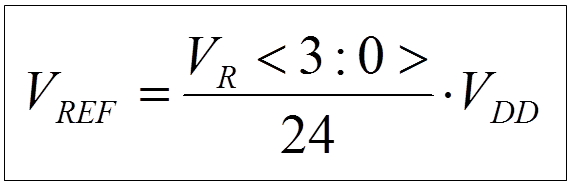

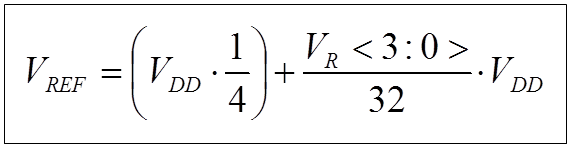

As equações utilizadas para calcular a saída do módulo de Referência de Tensão são as seguintes:

Se VRR = 1:

Se VRR = 0:

O tempo de ativação do módulo de Referência de Tensão deve ser considerado ao se alterar a saída da VREF (Tabela 17.3). O Exemplo 11.1 demonstra como a referência de tensão é configurada para uma tensão de saída de 1,25 V com VDD = 5,0 V.

|

|

|

R/W-0 |

R/W-0 |

R/W-0 |

U-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

|

VREN |

VROE |

VRR |

--- |

VR3 |

VR2 |

VR1 |

VR0 |

|

bit 7 |

|

|

|

|

|

|

bit 0 |

|

|

bit 7 |

VREN: Bit de Habilitação da VREF |

|

|

1 = Circuito da VREF ligado |

|

|

0 = Circuito da VREF desligado, sem dreno IDD

|

|

bit 6 |

VROE: Bit de Habilitação da Saída da VREF |

|

|

1 = VREF tem saída no pino RA2 |

|

|

0 = VREF está desconectada do pino RA2

|

|

bit 5 |

VRR: Bit de Seleção do Intervalo de VREF |

|

|

1 = Intervalo de valores baixos |

|

|

0 = Intervalo de valores altos

|

bit 4

|

Não implementado: Lido como '0'

|

|

bit 3-0 |

VR<3:0>: Bits de Seleção do Valor de VREF 0 ≤ VR<3:0> ≤ 15 |

|

|

Quando VRR = 1: VREF = (VR<3:0>/24) * VDD |

|

|

Quando VRR = 0: VREF = 1/4 * VDD + (VR<3:0>/32) * VDD

|

|

|

Legenda:

R = bit de leitura

W = bit de escrita

U = bit não implementado (unimplemented), lido como '0'

-n = valor na POR

'1' = bit está ativado

'0' = bit está apagado

x = bit é desconhecido |

MOVLW 0x02 ;4 entradas multiplexadas

MOVWF CMCON ;em dois comparadores.

BSF STATUS,RP0 ;Selecionar banco 1

MOVLW 0x07 ;RA3-RA0 são configuradas

MOVWF TRISA ;como saídas

MOVLW 0xA6 ;Habilita VREF

MOVWF VRCON ;Configurado intervalo baixo com VR<3:0>=6

BCF STATUS,RP0 ;Selecionar banco 0

CALL DELAY10 ;delay de 10μs

11.2 Precisão/Erro da Referência de Tensão

O intervalo completo de VSS até VDD não pode ser abrangido devido à construção do módulo. Os transistores nas partes superior e inferior da rede de resistores em escada (Figura 11.1) impedem a VREF de se aproximar de VSS ou de VDD. O módulo de Referência de Tensão é derivado de VDD, e portanto a saída da VREF se altera com as flutuações de VDD. A precisão absoluta testada do módulo de Referência de Tensão pode ser encontrada na Tabela 17.3.

11.3 Operação durante a Hibernação

Quando o equipamento é removido da Hibernação através de uma interrupção ou de uma pausa no Temporizador Cão-de-Guarda, o conteúdo do registrador VRCON não é afetado. Para que o consumo de energia no modo de Hibernação seja minimizado, o módulo de Referência de Tensão deve ser desabilitado.

11.4 Efeitos de uma Reinicialização

A reinicialização do equipamento desabilita o módulo de Referência de Tensão, apagando o bit VREN (VRCON<7>). Esta reinicialização também desconecta a referência do pino RA2, apagando o bit VROE (VRCON<6>) e seleciona o intervalo de valores altos de tensão, apagando o bit VRR (VRCON<5>). Os bits de seleção do valor de VREF, VRCON<3:0>, também são apagados.

11.5 Considerações sobre Conexão

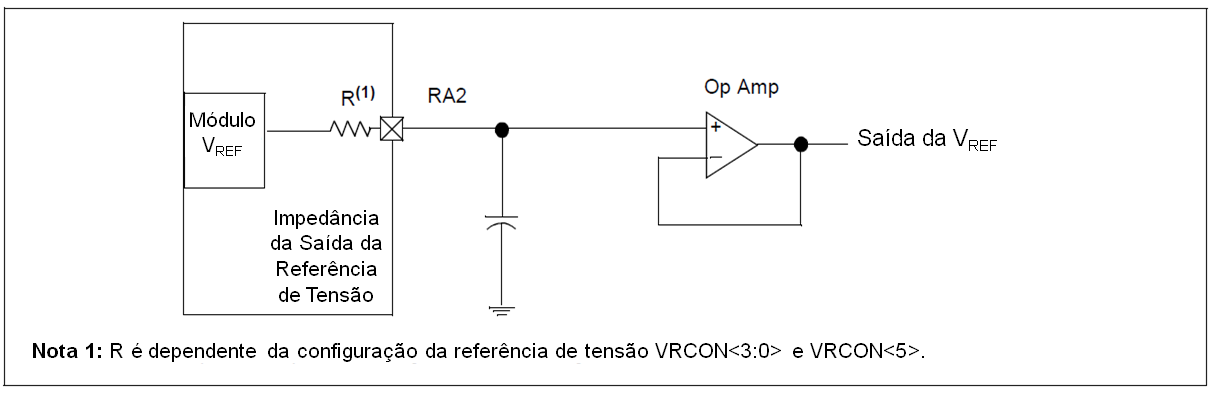

O módulo de Referência de Tensão opera independentemente do módulo Comparador. A saída do gerador de referência deve estar conectada ao pino RA2 se o bit TRISA<2> estiver ativado, e se o bit VROE, VRCON<6>, estiver ativado. A habilitação da saída do módulo de Referência de Tensão para o pino RA2 com um sinal de entrada presente aumentará o consumo de energia. A conexão do RA2 como saída digital com a VREF habilitada também aumentará o consumo de energia.

O pino RA2 pode ser utilizado como uma saída simples D/A (digital para analógica), com uma capacidade de direcionamento limitada. Devido à capacidade de direcionamento limitada, um buffer deve ser utilizado em conjunto com a saída do módulo de Referência de Tensão, para conexões externas com a VREF. A Figura 11.2 mostra um exemplo de buffer.

TABELA 11.1: REGISTRADORES ASSOCIADOS À REFERÊNCIA DE TENSÃO

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

9Fh |

VRCON |

VREN |

VROE |

VRR |

--- |

VR3 |

VR2 |

VR1 |

VR0 |

000- 0000 |

000- 0000 |

|

1Fh |

CMCON |

C2OUT |

C1OUT |

C2INV |

C1INV |

CIS |

CM2 |

CM1 |

CM0 |

0000 0000 |

0000 0000 |

|

85h |

TRISA |

TRISA7 |

TRISA6 |

TRISA5 |

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

1111 1111 |

1111 1111 |

Legenda: - = não implementado, lido como '0'