Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

O módulo CCP (Capture/Compare/PWM = Captura/Comparação/Modulação por Largura de Pulso) dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A contém um registrador de 16 bits que pode operar como um registrador de Captura de 16 bits, como um registrador de Comparação de 16 bits, ou como um como um registrador de Ciclo de Trabalho (Duty Cycle) mestre/escravo da PWM. A Tabela 9.1 apresenta os recursos de temporizador dos modos do módulo CCP.

Módulo CCP1

O Register1 de Captura/Comparação/PWM (CCPR1) é composto de dois registradores de 8 bits: CCPR1L (byte baixo) e CCPR1H (byte alto). O registrador CCP1CON controla a operação do CCP1. Todos são acessíveis para leitura e escrita.

Informações adicionais sobre o módulo CCP estão disponíveis no "Manual de Referência da Família de MCUs de Média Ordem PIC®" (DS33023).

|

Modo CCP |

Recurso de Temporizador |

|

Captura |

Timer1 |

|

Comparação |

Timer1 |

|

PWM |

Timer2 |

|

|

|

U-0 |

U-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

|

--- |

--- |

CCP1X |

CCP1Y |

CCP1M3 |

CCP1M2 |

CCP1M1 |

CCP1M0 |

|

bit 7 |

|

|

|

|

|

|

bit 0 |

|

bit 7-6

|

Não Implementados: Lidos como '0'

|

|

bit 5-4 |

CCP1X:CCP1Y: Bits Menos Significativos da PWM |

|

|

Modo Captura |

|

|

Não utilizado |

|

|

Modo Comparação |

|

|

Não utilizado |

|

|

Modo PWM |

|

|

Estes bits são os dois LSbs (bits menos significativos) do ciclo de trabalho da PWM. Os oito MSbs (bits mais significativos) encontram-se no CCPRxL.

|

|

bit 3-0 |

CCP1M<3:0>: Bits de Seleção do Modo CCPx |

|

|

0000 = Captura/Comparação/PWM desligado(reinicializa o módulo CCP1) |

|

|

0100 = modo Captura, a cada borda de descida |

|

|

0101 = modo Captura, a cada borda de subida |

|

|

0110 = modo Captura, a cada 4ª borda de subida |

|

|

0111 = modo Captura, a cada 16ª borda de subida |

|

|

1000 = modo Comparação, ativa a saída no match (equivalência) (o bit CCP1IF é ativado) |

|

|

1001 = modo Comparação, apaga a saída na equivalência (o bit CCP1IF é ativado) |

|

|

1010 = modo Comparação, gera interrupção do software na equivalência (o bit CCP1IF é ativado, o pino CCP1 não é afetado) |

|

|

1011 = modo Comparação, dispara evento especial (o bit CCP1IF é ativado; o CCP1 reinicializa o TMR1) |

|

|

11xx = Modo PWM

|

|

|

Legenda:

R = bit de leitura

W = bit de escrita

U = bit não implementado (unimplemented), lido como '0'

-n = valor na POR

'1' = bit está ativado

'0' = bit está apagado

x = bit é desconhecido |

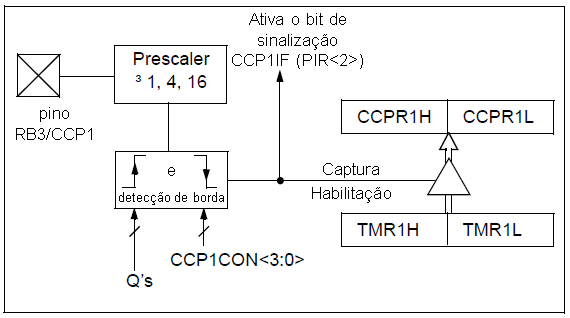

9.1 Modo Captura

No modo Captura, o CCPR1H:CCPR1L captura o valor de 16 bits do registrador TMR1 quando um evento ocorre no pino RB3/CCP1. Um evento é definido como:

-

Cada borda de descida

-

Cada borda de subida

-

Cada 4ª borda de subida

-

Cada 16ª borda de subida

Um evento é selecionado pelos bits de controle CCP1M<3:0> (CCP1CON<3:0>). Quando uma captura é realizada, o bit sinalizador de solicitação de interrupção CCP1IF (PIR<2>) é ativado. Ele deve ser apagado pelo software. Se uma outra captura ocorre antes da leitura do valor no registrador CCPR1, o valor previamente capturado será perdido.

9.1.1 CONFIGURAÇÃO DO PINO CCP

No modo Captura, o pino RB3/CCP1 deve ser configurado como saída ativando-se o bit TRISB<3>.

Nota:

Se o RB3/CCP1 estiver configurado como saída, uma escrita na porta pode causar uma condição de captura.

FIGURA 9.1: DIAGRAMA DE BLOCOS DA OPERAÇÃO NO MODO CAPTURA

9.1.2 SELEÇÃO DO MODO DO TIMER1

O Timer1 deve estar operando no modo Temporizador ou no modo Contador Sincronizado para que o módulo CCP utilize a propriedade de captura. No modo Contador Assíncrono, a operação de captura pode não funcionar.

9.1.3 INTERRUPÇÃO DO SOFTWARE

Quando o modo Captura é alterado, uma falsa interrupção da captura pode ser gerada. O usuário deve manter o bit CCP1IE (PIE<2>) apagado a fim de evitar falsas interrupções, e deve apagar o bit sinalizador CCP1IF depois de qualquer alteração deste tipo no modo de Operação.

9.1.4 PRÉ-SCALER DO CCP

Existem quatro configurações do pré-scaler, especificadas pelos bits CCP1M<3:0>. Sempre que o módulo CCP estiver desligado, ou não estiver no modo Captura, o contador do pré-scaler é apagado. Isto significa que qualquer reinicialização apagará o contador do pré-scaler.

A troca de um pré-scaler de captura para outro pode gerar uma interrupção. Além disso, o contador do pré-scaler não será apagado, e portanto a primeira captura deve ser de um pré-scaler com valor diferente de zero. O Exemplo 9.1 apresenta o método recomendado para a troca de pré-scaler de captura. Este método também apaga o contador do pré-scaler de forma a não gerar a "falsa" interrupção.

CLRF CCP1CON ;Desativa o módulo CCP

MOVLW NEW_CAPT_PS ;Carrega no registrador W o novo valor

;e modo do pré-scaler e ativa o CCP

MOVWF CCP1CON ;Carrega o novo valor em CCP1CON

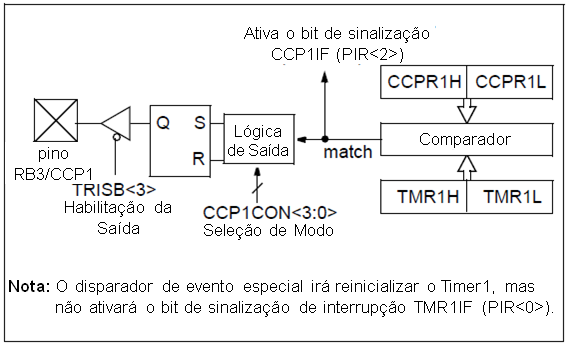

9.2 Modo Comparação

No modo Comparação, o valor do registrador de 16 bits CCPR1 é constantemente comparado com o valor do par de registradores TMR1. Quando ocorre uma equivalência (match), o pino RB3/CCP1 é:

-

Conduzido ao nível alto

-

Conduzido ao nível baixo

-

Mantido sem alteração

A ação no pino é baseada no valor dos bits de controle CCP1M<3:0> (CCP1CON<3:0>). Ao mesmo tempo, o bit de sinalização de interrupção CCP1IF é ativado.

FIGURA 9.2: DIAGRAMA DE BLOCOS DA OPERAÇÃO NO MODO COMPARAÇÃO

9.2.1 CONFIGURAÇÃO DE PINOS DO CCP

O usuário deve configurar o pino RB3/CCP1 como saída, apagando o bit TRISB<3>.

Nota:

Ao se apagar o registrador CCP1CON, a latch de saída de comparação do RB3/CCP1 será forçada ao nível padrão, baixo. Esta não é a latch de dados.

9.2.2 SELEÇÃO DO MODO DO TIMER1

O Timer1 deve estar operando no modo Temporizador ou no modo Contador Sincronizado se o módulo CCP estiver utilizando a propriedade de comparação. No modo Contador Assíncrono, a operação de comparação pode não funcionar.

9.2.3 MODO DE INTERRUPÇÃO DO SOFTWARE

Quando se opta pela geração de uma interrupção do software, o pino CCP1 não é afetado. É gerada somente uma interrupção do CCP (se habilitada).

Neste Modo (CCPM<3:0>=1001), é gerado um trigger (disparador) interno do hardware, o qual pode ser utilizado para iniciar uma ação. Veja o Registrador 9.1.

A saída do disparador de evento especial do CCP ocorre imediatamente no caso de um match (equivalência) entre o par de registradores TMR1H, TMR1L e o par de registradores CCPR1H, CCPR1L. O par de registradores TMR1H, TMR1L não é reinicializado até a próxima borda de subida do clock TMR1. Isso permite que o par de registradores CCPR1 seja efetivamente um registrador de período de 16 bits programável para o Timer1. A saída do disparador de evento especial também inicia uma conversão A/D, tendo em vista que o módulo A/D está habilitado.

Nota:

A remoção da condição de match através da troca do conteúdo do par de registradores CCPR1H, CCPR1L entre a borda do clock que gera o disparador de evento especial e a borda do clock que gera a Reinicialização do TMR1 impedirá a ocorrência da reinicialização.

TABELA 9.2: REGISTRADORES ASSOCIADOS À CAPTURA, COMPARAÇÃO E TIMER1

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

0Bh, 8Bh, 10Bh, 18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

8Ch |

PIE1 |

EEIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

0000 -000 |

|

86h, 186h |

TRISB |

Registrador de Direcionamento de Dados da PORTB |

1111 1111 |

1111 1111 |

|

0Eh |

TMR1L |

Holding Register para o Byte Menos Significativo do Registrador de 16 bits TMR1 |

xxxx xxxx |

uuuu uuuu |

|

0Fh |

TMR1H |

Holding Register para o Byte Mais Significativo do Registrador de 16 bits TMR1 |

xxxx xxxx |

uuuu uuuu |

|

10h |

T1CON |

--- |

--- |

T1CKPS1 |

T1CKPS0 |

T1OSCEN |

T1SYNC |

TMR1CS |

TMR1ON |

--00 0000 |

--uu uuuu |

|

15h |

CCPR1L |

Register1 de Captura/ Comparação/ PWM (LSB) |

xxxx xxxx |

uuuu uuuu |

|

16h |

CCPR1H |

Register1 de Captura/ Comparação/ PWM (MSB) |

xxxx xxxx |

uuuu uuuu |

|

17h |

CCP1CON |

--- |

--- |

CCP1X |

CCP1Y |

CCP1M3 |

CCP1M2 |

CCP1M1 |

CCP1M0 |

--00 0000 |

--00 0000 |

Legenda:

x = desconhecido

u = inalterado

- = não implementado, lido como '0'

células sombreadas = não utilizadas pela Captura e Timer1

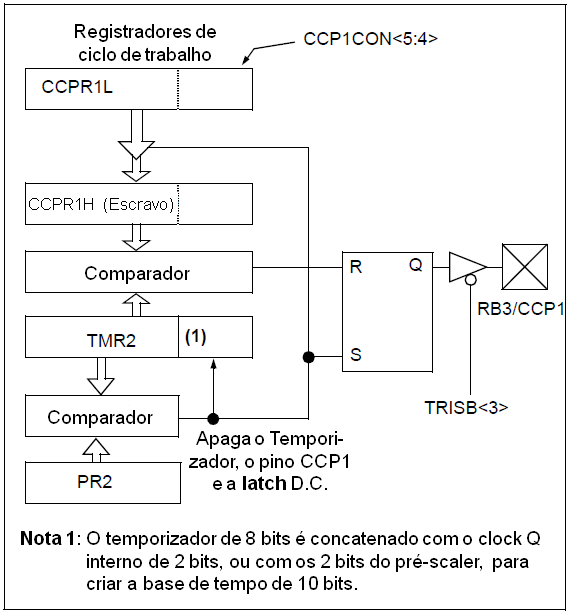

9.3 Modo PWM

No modo Modulação por Largura de Pulso (Pulse Width Modulation = PWM), o pino CCP1 produz uma saída de PWM com resolução de até 10 bits. Como o pino CCP1 é multiplexado com a latch de dados da PORTB, o bit TRISB<3> deve ser apagadp para tornar o pino CCP1 uma saída.

Nota:Ao se apagar o registrador CCP1CON, a latch de saída de PWM do CCP1 será forçada ao nível padrão, baixo. Esta não é a latch de dados de I/O da PORTB.

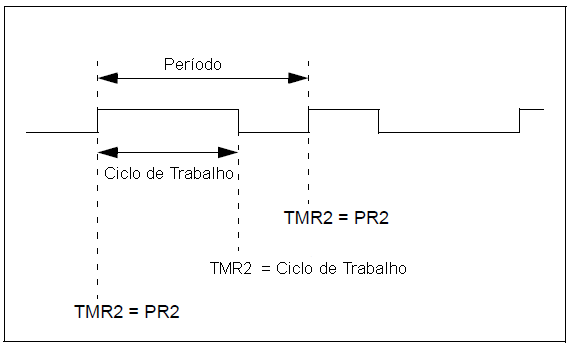

A Figura 9.3 apresenta um diagrama de blocos simplificado do módulo CCP no modo PWM.

Para o passo-a-passo do procedimento de configuração do módulo CCP para uma operação da PWM, veja a Seção 9.3.3 "Configuração para a Operação da PWM".

Uma saída de PWM (Figura 9.4) tem uma base de tempo (período) e um tempo em que a saída permanece alta (duty cycle = ciclo de trabalho). A frequência da PWM é o inverso do período (frequência = 1/período).

9.3.1 PERÍODO DA PWM

O período da PWM é especificado através da escrita no registrador PR2. O período da PWM pode ser calculado utilizando-se a seguinte fórmula:

A frequência da PWM é definida como 1/[período da PWM].

Quando o TMR2 é igual ao PR2, os três eventos seguintes ocorrem no ciclo de incrementação seguinte:

-

O TMR2 é apagado

-

O pino CCP1 é ativado (exceção: se o ciclo de trabalho da PWM = 0%, o pino CCP1 não será ativado)

-

O ciclo de trabalho da PWM é transferido do CCPR1L para o CCPR1H

Nota:O pós-scaler do Timer2 (veja a

Seção 8.0 "Módulo Timer2") não é utilizado na determinação da frequência da PWM. O pós-scaler poderia ser utilizado para se obter uma taxa de atualização do servo em uma frequência diferente daquela da saída de PWM.

9.3.2 DUTY CYCLE DA PWM

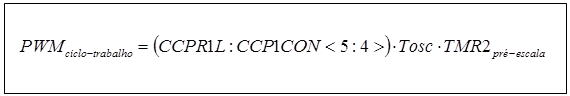

O duty cycle (ciclo de trabalho) da PWM é especificado através da escrita no registrador CCPR1L e nos bits CCP1CON<5:4>.Uma resolução de até 10 bits está disponível: o CCPR1L contém os 8 MSbs (Most Significant bits = bits mais significativos) e o CCP1CON<5:4> contém os 8 LSbs (Least Significant bits = bits menos significativos). Este valor de 10 bits é representado pelos CCPR1L:CCP1CON<5:4>.A seguinte equação é utilizada para calcular o ciclo de trabalho da PWM em unidade de tempo:

O CCPR1L e os CCPRCON<5:4> podem receber operações de escrita a qualquer tempo, mas o ciclo de trabalho não é armazenado no CCPR1H até que ocorra um match (equivalência) entre o PR2 e o TMR2 (i.e., que o período seja completado). No modo PWM, o registrador CCPR1H é acessivel somente para leitura.

O registrador CCPR1H e uma latch interna de 2 bits são utilizados para o armazenamento temporário duplo do ciclo de trabalho da PWM. Este armazenamento temporário duplo é essencial para a ausência de falhas na operação de PWM.

Quando ocorre a equivalência entre CCPR1H e a latch de 2 bits, e TMR2, concatenado com 2 bits do clock Q interno ou 2 bits do pré-scaler do TMR2, o pino CCP1 é apagado.

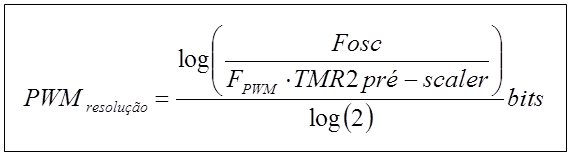

Resolução máxima da PWM (em bits) para uma dada frequência da PWM:

Nota: Se o valor do ciclo de trabalho da PWM for mais longo do que o período da PWM, o pino CCP1 não será apagado.

Para um exemplo de cálculo de período e ciclo de trabalho da PWM, consulte o "Manual de Referência da Família de MCUs de Média Ordem PIC®" (DS33023).

Os seguintes passos devem ser seguidos ao se configurar o módulo CCP para a operação de PWM:

-

Ativar o período da PWM através da escrita no registrador PR2.

-

Ativar o ciclo de trabalho da PWM através da escrita no registrador CCPR1L e nos bits CCP1CON<5:4>.

-

Tornar o pino CCP1 uma saída apagando-se o bit TRISB<3>.

-

Ajustar o valor da pré-escala do TMR2 e habilitar o Timer2 através da escrita no T2CON.

TABELA 9.3: EXEMPLOS DE FREQUÊNCIAS E RESOLUÇÕES EM 20 MHz

|

Frequência da PWM |

1,22 kHz |

4,88 kHz |

19,53 kHz |

78,12 kHz |

156,3 kHz |

208,3 kHz |

|

Pré-scaler do Timer (1,4,16) |

16 |

4 |

1 |

1 |

1 |

1 |

|

Valor do PR2 |

0xFF |

0xFF |

0xFF |

0x3F |

0x1F |

0x17 |

|

Resolução Máxima (bits) |

10 |

10 |

10 |

8 |

7 |

6,5 |

TABELA 9.4: REGISTRADORES ASSOCIADOS À PWM E AO TIMER2

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

0Bh, 8Bh, 10Bh, 18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

8Ch |

PIE1 |

EEIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

0000 -000 |

|

86h, 186h |

TRISB |

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

1111 1111 |

1111 1111 |

|

11h |

TMR2 |

Registrador do Módulo Timer2 |

0000 0000 |

0000 0000 |

|

92h |

PR2 |

Registrador de Período do Módulo Timer2 |

1111 1111 |

1111 1111 |

|

12h |

T2CON |

--- |

TOUTPS3 |

TOUTPS2 |

TOUTPS1 |

TOUTPS0 |

TMR2ON |

T2CKPS1 |

T2CKPS0 |

-000 0000 |

uuuu uuuu |

|

15h |

CCPR1L |

Register1 de Captura/ Comparação/ PWM (LSB) |

xxxx xxxx |

uuuu uuuu |

|

16h |

CCPR1H |

Register1 de Captura/ Comparação/ PWM (MSB) |

xxxx xxxx |

uuuu uuuu |

|

17h |

CCP1CON |

--- |

--- |

CCP1X |

CCP1Y |

CCP1M3 |

CCP1M2 |

CCP1M1 |

CCP1M0 |

--00 0000 |

--00 0000 |

Legenda:

x = desconhecido

u = inalterado

- = não implementado, lido como '0'

células sombreadas = não utilizadas pela Captura e Timer2