Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possuem duas portas, PORTA e PORTB. Alguns pinos para estas portas I/O são multiplexados com funções alternativas para as propriedades dos periféricos no dispositivo. Em geral, quando um periférico é habilitado, aquele pino não pode ser utilizado como um pino I/O de propósito genérico.

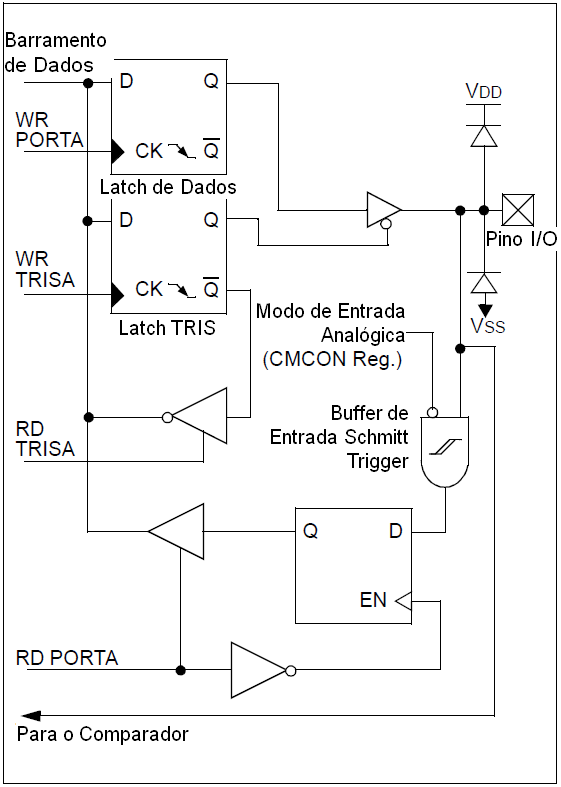

A PORTA consiste em uma latch com 8 bits de largura. A RA4 é uma entrada do tipo Schmitt Trigger e uma saída de dreno aberto. A porta RA4 é multiplexada com a entrada de clock T0CKI. A RA5(1) é somente uma entrada tipo Schmitt Trigger e não possui drivers de saída. Todos os outros pinos de porta RA possuem níveis de entrada tipo Schmitt Trigger e drivers de saída CMOS completos. Todos os pinos possuem bits de direcionamento de dados (registradores TRIS) que podem configurá-los como entrada ou saída.

Um '1' no registrador TRISA coloca o driver de saída correspondente em modo de Alta Impedância. Um '0' no registrador TRISA coloca o conteúdo da latch de saída no(s) pino(s) selecionado(s).

A leitura do registrador PORTA detecta o status dos pinos, assim como a escrita irá salvar na latch da porta. Todas as operações de escrita são do tipo leitura-modificação-escrita. Então uma escrita em uma porta implica no fato de os pinos da mesma serem primeiramente lidos, e em seguida este valor ser modificado e escrito na latch de dados da porta.

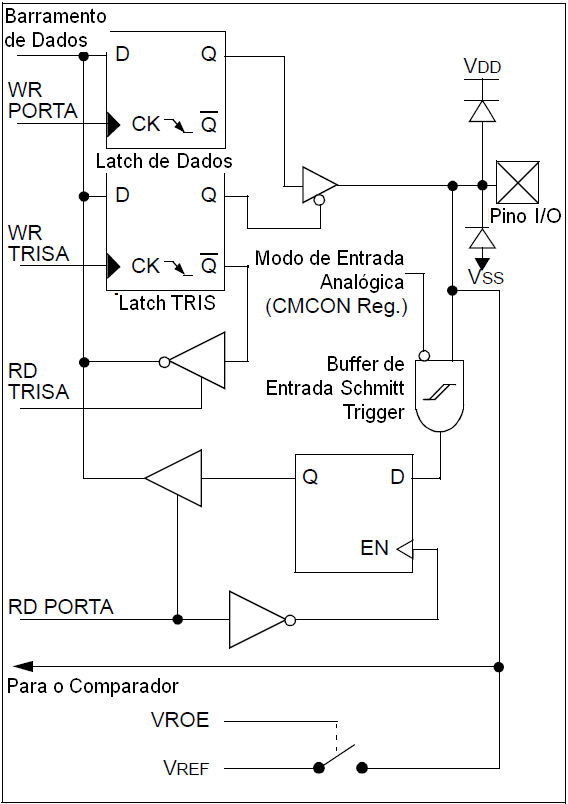

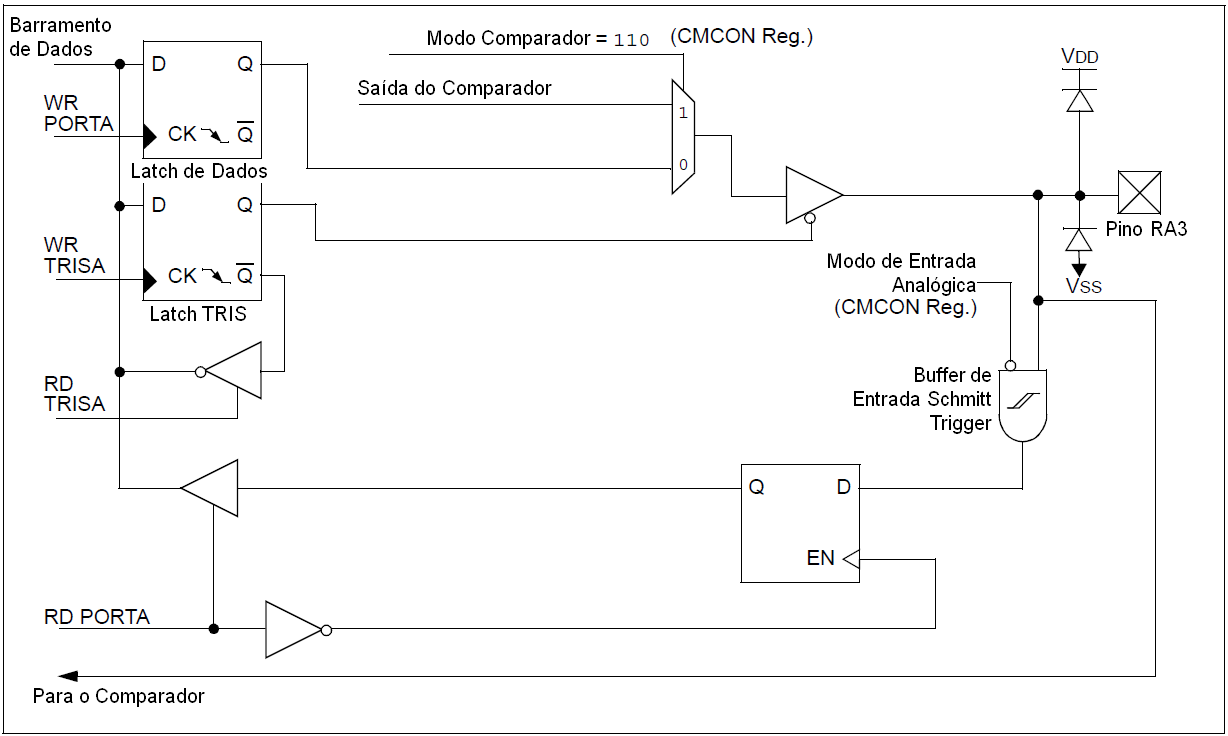

Os pinos da PORTA são multiplexados com funções de comparador e de referência de tensão. A operação destes pinos é selecionada por bits de controle no registrador CMCON (registrador de Controle de Comparação) e no registrador VRCON (registrador de Controle de Referência de Tensão). Quando selecionados como entrada de comparador, estes pinos serão lidos como '0's.

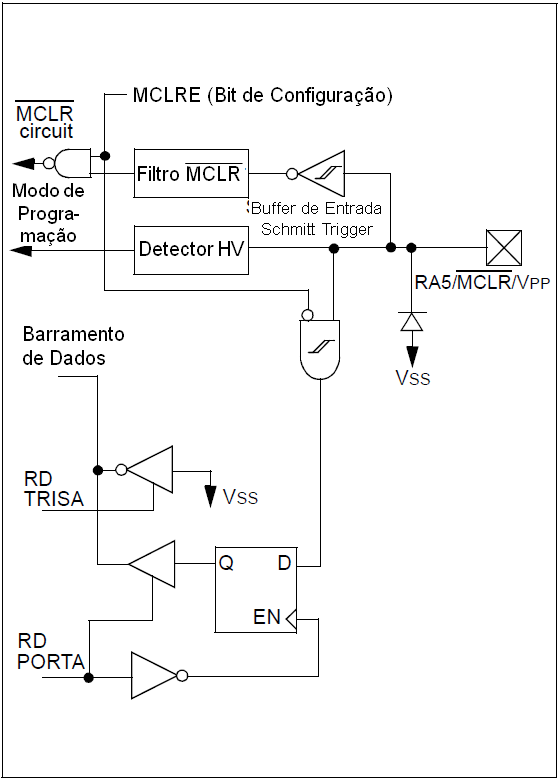

Nota 1:

A RA5 divide sua função com a VPP. Quando os níveis de voltagem da VPP são aplicados à RA5, o dispositivo entrará no modo de Programação.

Nota 2:

Na reinicialização, o registrador TRISA é ativado para todas as entradas. As entradas digitais (RA<3:0>) são desabilitadas e as entradas do comparador são forçadas a parar a fim de reduzir o consumo de energia.

Nota 3:

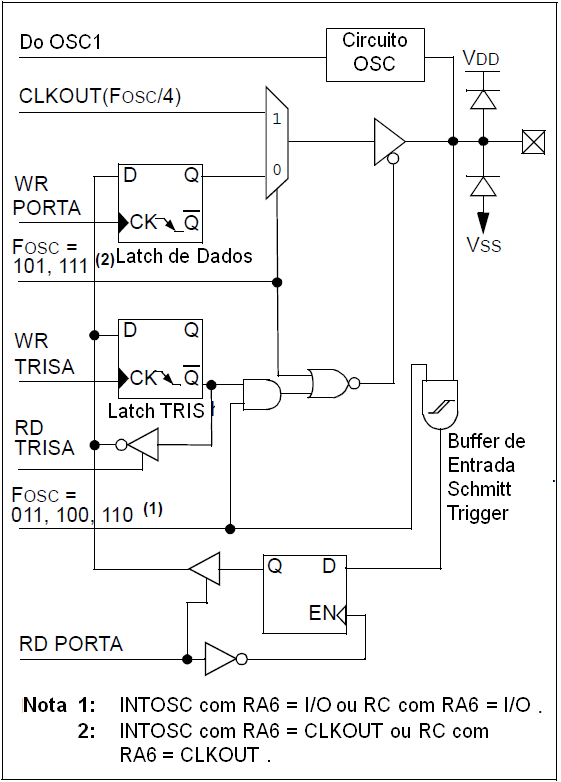

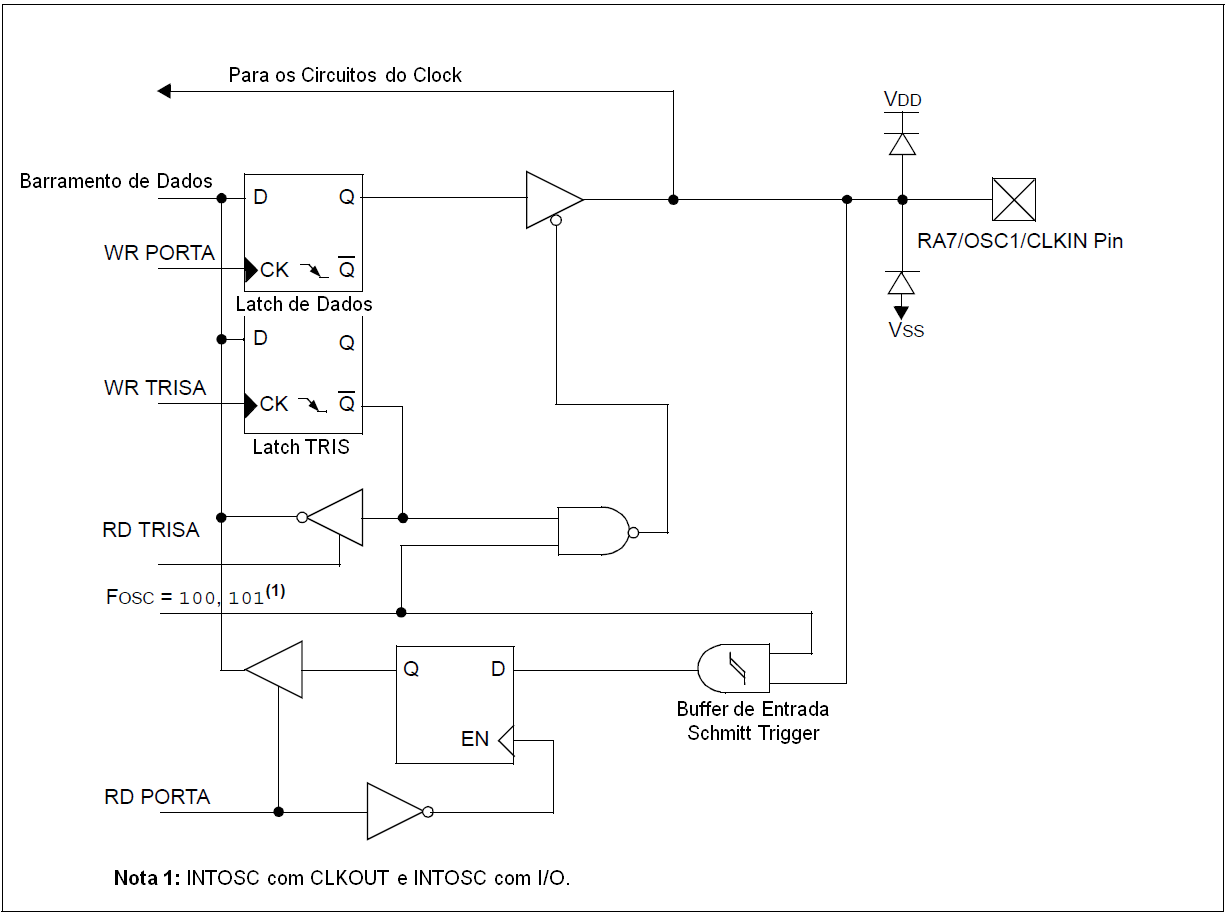

Os bits TRISA<6:7> são sobrepostos pela configuração do oscilador. Quando os bits PORTA<6:7> são sobrepostos, os dados são lidos como '0' e os bits TRISA<6:7> são ignorados.

TRISA controla a direção dos pinos da RA, mesmo quando eles estão sendo utilizados como entradas de comparador. O usuário deve assegurar-se de manter os pinos configurados como entradas quando utilizá-los como entradas do comparador.

O pino RA2 também funcionará como saída para a referência de tensão. Quando neste modo, o pino VREF consiste em uma saída de impedância muito alta. O usuário deve configurar o bit TRISA<2> como saída e utilizar cargas de alta impedância.

Em um dos modos de comparador definidos pelo registrador CMCON, os pinos RA3 e RA4 se tornam saídas dos comparadores. Os bits TRISA<4:3> devem ser apagados a fim de habilitar as saídas a utilizar esta função.

EXEMPLO 5.1: INICIALIZANDO A PORTA

CLRF PORTA ;Inicialização da porta pela preparação

;das latches de saída de dados

MOVLW 0x07 ;Desligar os comparadores e

MOVWF CMCON ;habilitar os pinos para funções de entrada e saída

BCF STATUS, RP1

BSF STATUS, RP0 ;Selecionar o banco 1

MOVLW 0x1F ;Valor usado para inicializar o direcionamento dos dados

MOVWF TRISA ;Define RA<4:0> como entradas

;TRISA<5> é sempre lido como '1'

;TRISA<7:6> depende do modo do oscilador

FIGURA 5.1: DIAGRAMA DE BLOCOS DOS PINOS RA0/AN0:RA1/AN1

FIGURA 5.2: DIAGRAMA DE BLOCOS DO PINO RA2/AN2/VREF

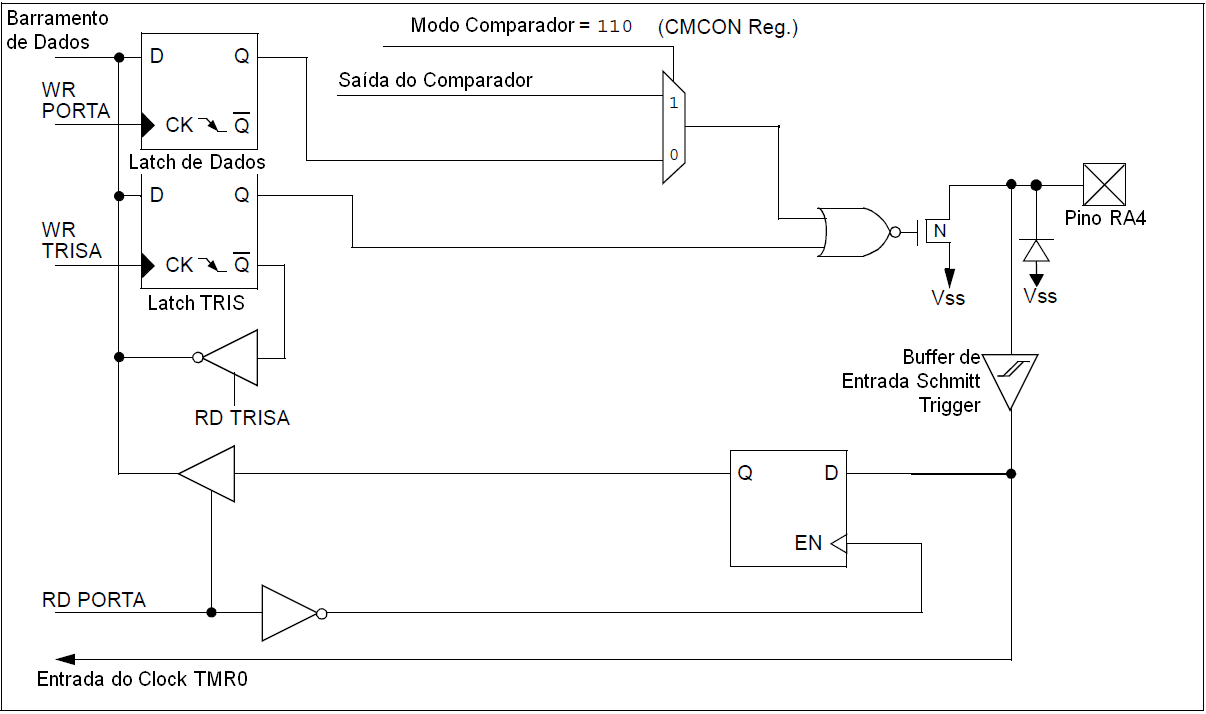

FIGURA 5.3: DIAGRAMA DE BLOCOS DO PINO RA3/AN3/CMP1

FIGURA 5.5: DIAGRAMA DE BLOCOS DO PINO RA5/MCLR/VPP

FIGURA 5.6: DIAGRAMA DE BLOCOS DO PINO RA6/OSC2/CLKOUT

FIGURA 5.7: DIAGRAMA DE BLOCOS DO PINO RA7/OSC1/CLKIN

TABELA 5.1: FUNÇÕES DA PORTA

|

Nome |

Função |

Tipo de Entrada |

Tipo de Saída |

Descrição |

|

RA0/AN0 |

RA0 |

ST |

CMOS |

Porta de entrada/saída bidirecional |

|

AN0 |

AN |

--- |

Entrada do comparador analógico |

|

RA1/AN1 |

RA1 |

ST |

CMOS |

Porta de entrada/saída bidirecional |

|

AN1 |

AN |

--- |

Entrada do comparador analógico |

|

RA2/AN2/VREF |

RA2 |

ST |

CMOS |

Porta de entrada/saída bidirecional |

|

AN2 |

AN |

--- |

Entrada do comparador analógico |

|

VREF |

--- |

AN |

Saída da VREF |

|

RA3/AN3/CMP1 |

RA3 |

ST |

CMOS |

Porta de entrada/saída bidirecional |

|

AN3 |

AN |

--- |

Entrada do comparador analógico |

|

CMP1 |

--- |

CMOS |

Saída do comparador 1 |

|

RA4/T0CKI/CMP2 |

RA4 |

ST |

OD |

Porta de entrada/ saída bidirecional. A saída é do tipo dreno aberto. |

|

T0CKI |

ST |

--- |

Entrada de clock externo para o TMR0 ou saída do comparador |

|

CMP2 |

--- |

OD |

Saída do comparador 2 |

|

RA5/MCLR/VPP |

RA5 |

ST |

--- |

Porta de entrada |

|

MCLR |

ST |

--- |

Limpeza principal. Quando configurado como MCLR, este pino representa uma reinicialização inferior ativa do dispositivo. A voltagem no MCLR/VPP não pode exceder a VDD durante a operação normal do dispositivo. |

|

VPP |

HV |

--- |

Entrada de voltagem de programação |

|

RA6/OSC2/CLKOUT |

RA6 |

ST |

CMOS |

Porta de entrada/ saída bidirecional |

|

OSC2 |

--- |

XTAL |

Saída do oscilador de cristal. Se conecta com o ressonador de cristal no modo Oscilador de Cristal |

|

CLKOUT |

--- |

CMOS |

No modo RC ou INTOSC. O pino OSC2 pode ser a saída CLKOUT, o qual tem 1/4 da frequência do OSC1 |

|

RA7/OSC1/CLKIN |

RA7 |

ST |

CMOS |

Porta de entrada/ saída bidirecional |

|

OSC1 |

XTAL |

--- |

Entrada do oscilador de cristal. Se conecta com o ressonador de cristal no modo Oscilador de Cristal |

|

CLKIN |

ST |

--- |

Entrada da fonte de clock externa. Pino de polarização RC. |

Legenda:

O = Saída (output)

CMOS = Saída CMOS

P = Energia (power)

--- = não utilizado(a)

I = Entrada (input)

ST = Entrada tipo Schmitt Trigger

TTL = Entrada TTL

OD = Saída de dreno aberto (open drain)

AN = analógico(a)

TABELA 5.2: RESUMO DOS REGISTRADORES ASSOCIADOS À PORTA

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

05h |

PORTA |

RA7 |

RA6 |

RA5(1) |

RA4 |

RA3 |

RA2 |

RA1 |

RA0 |

xxxx 0000 |

qqqu 0000 |

|

85h |

TRISA |

TRISA7 |

TRISA6 |

TRISA5 |

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

1111 1111 |

1111 1111 |

|

1Fh |

CMCON |

C2OUT |

C1OUT |

C2INV |

C1INV |

CIS |

CM2 |

CM1 |

CM0 |

0000 0000 |

0000 0000 |

|

9Fh |

VRCON |

VREN |

VROE |

VRR |

--- |

VR3 |

VR2 |

VR1 |

VR0 |

000- 0000 |

000- 0000 |

Legenda:

- = Posições não implementadas, lidas como '0'

u = inalterado

x = desconhecido

q = o valor depende da condição

células sombreadas = não utilizadas para a PORTA

Nota 1: O bit de configuração MCLRE ativa a funcionalidade do RA5.

A PORTB é uma porta bi-direcional com 8 bits de largura. O registrador de direcionamento de dados correspondente a ela é o TRISB. Um '1' no registrador TRISB coloca o driver de saída correspondente em modo de Alta Impedância. Um '0' no registrador TRISB coloca o conteúdo da latch de saída no(s) pino(s) selecionado(s).

A PORTB é multiplexada com os módulos de interrupção externa, USART e CCP e com a entrada/ saída de clock TMR1. As funções padrão, bem como as funções alternativas da porta são apresentadas na Tabela 5.3. As funções alternativas da porta podem se sobrepor à ativação do TRIS quando habilitadas.

A leitura do registrador PORTB detecta o status dos pinos, enquanto a escrita nele irá salvar na latch da porta. Todas as operações de escrita são do tipo ler-modificar-escrever. Então uma escrita em uma porta implica no fato de os pinos da mesma serem primeiramente lidos, e em seguida este valor ser modificado e escrito na latch de dados da porta.

Cada um dos pinos da PORTB tem um pull-up interno fraco (≈ 200 μA típica). Um único bit de controle pode acionar todos os pull-ups. Isto é feito apagando-se o bit RBPU (OPTION<7>). O pull-up fraco é automaticamente desligado quando o pino da porta é configurado como saída. Os pull-ups são desabilitados na Reinicialização de Power-on.

Quatro dos pinos da PORTB, RB<7:4>, possuem uma propriedade de interrupção na alteração (interrupt-on-change). Somente os pinos configurados como entrada podem causar a ocorrência desta interrupção (i.e., qualquer pino dentre os RB<7:4> configurado como saída é excluído da comparação interrupt-on-change). Os pinos de entrada (dentre os RB<7:4>) são comparados com o antigo valor armazenado na última leitura da PORTB. As saídas de "não-igualdade" dentre os RB<7:4> são agrupadas através do operador OU para gerar a interrupção do RBIF (sinalizador armazenado em INTCON<0>).

Esta interrupção pode retirar o dispositivo da Hibernação. O usuário pode, durante a rotina de interrupção, desativá-la da seguinte forma:

-

Qualquer leitura ou escrita na PORTB. Isso encerrará a condição de não-igualdade.

-

Apagar o bit sinalizador RBIF.

Uma condição de não-igualdade continuará a ativar o bit sinalizador RBIF. A leitura da PORTB encerrará a condição de não-igualdade e permitirá o bit sinalizador RBIF de ser apagado.

A propriedade de interrupção por não-igualdade, juntamente com os pull-ups configuráveis pelo software nestes quatro pinos permitem uma interface com o teclado facilitada e possibilita um aumento na velocidade de digitação.(Veja a Nota de Aplicação AN552 "Implementando um Aumento na Velocidade de Digitação" (DS00552)).

Nota:

Se uma alteração no pino I/O ocorrer quando uma operação de leitura estiver sendo executada (início do ciclo Q2), então o sinalizador de interrupção RBIF pode não ser ativado.

A propriedade interrupt-on-change é recomendada para aumentar a velocidade da operação de digitação e de operações nas quais a PORTB é utilizada somente para a propriedade interrupt-on-change. A inativação do PORTB não é recomendada durante a utilização da propriedade interrupt-on-change.

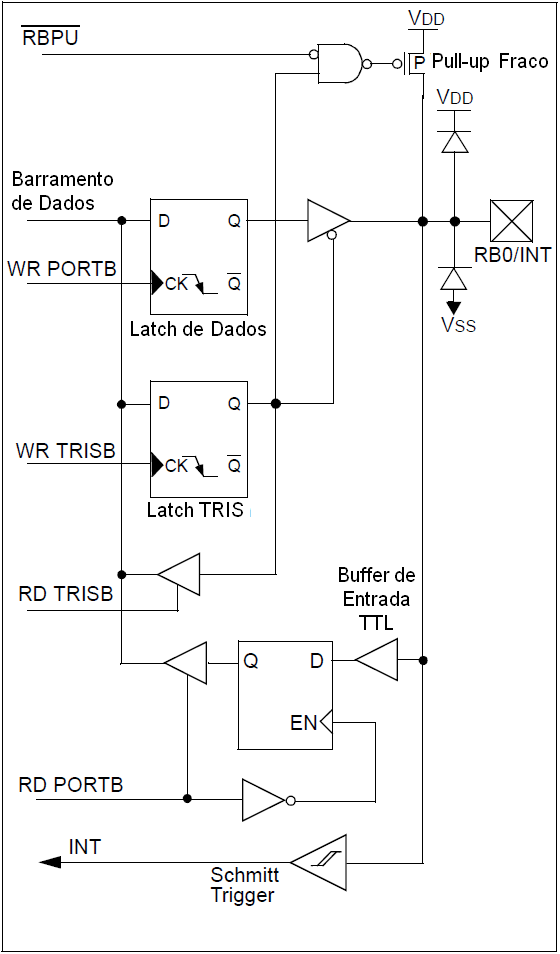

FIGURA 5.8: DIAGRAMA DE BLOCOS DO PINO RB0/INT

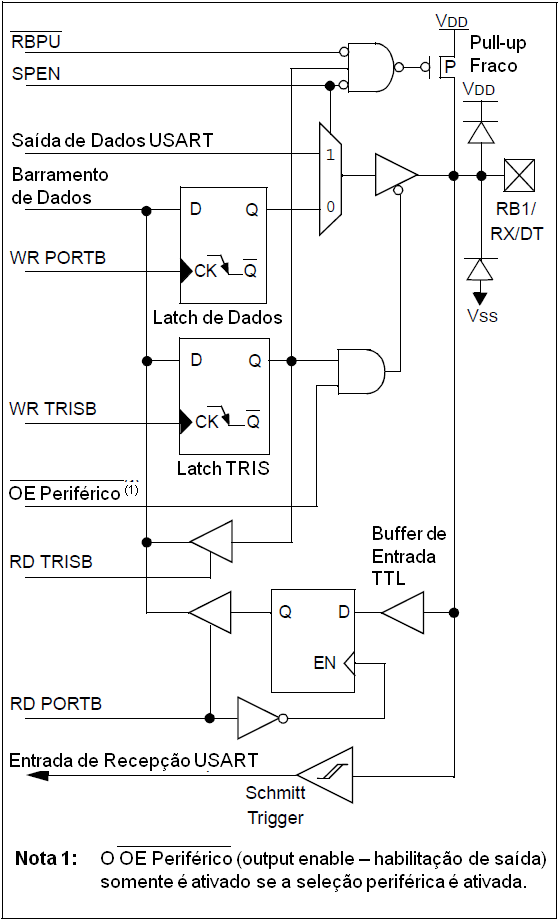

FIGURA 5.9: DIAGRAMA DE BLOCOS DO PINO RB1/RX/DT

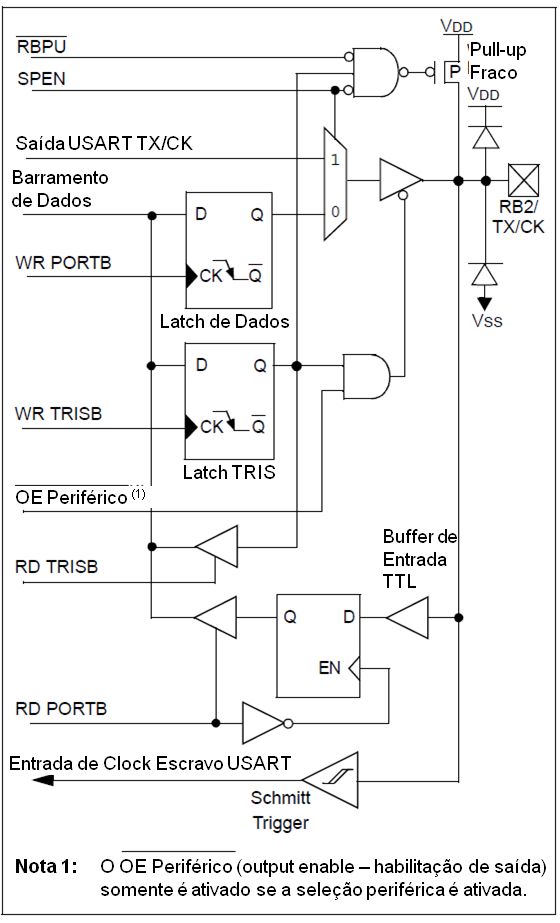

FIGURA 5.10: DIAGRAMA DE BLOCOS DO PINO RB2/TX/CK

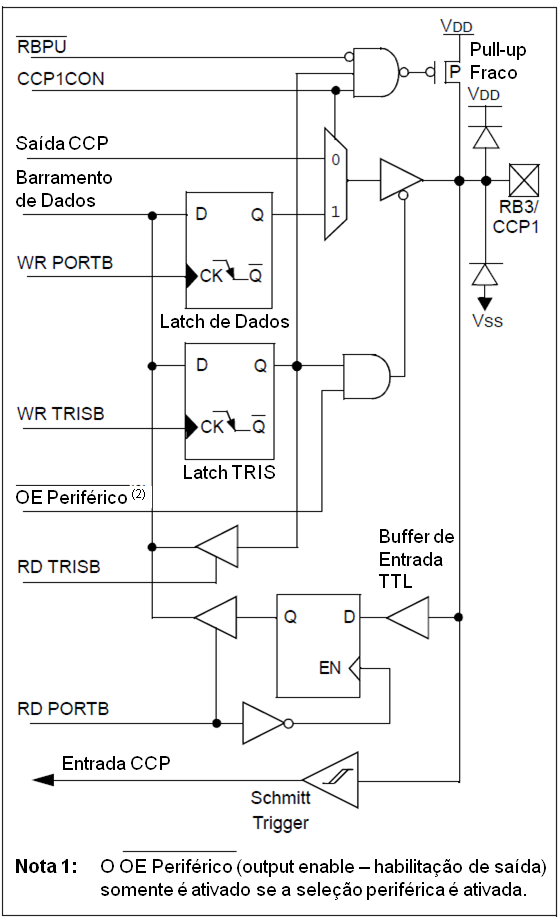

FIGURA 5.11: DIAGRAMA DE BLOCOS DO PINO RB3/CCP1

FIGURA 5.12: DIAGRAMA DE BLOCOS DO PINO RB4/PGM

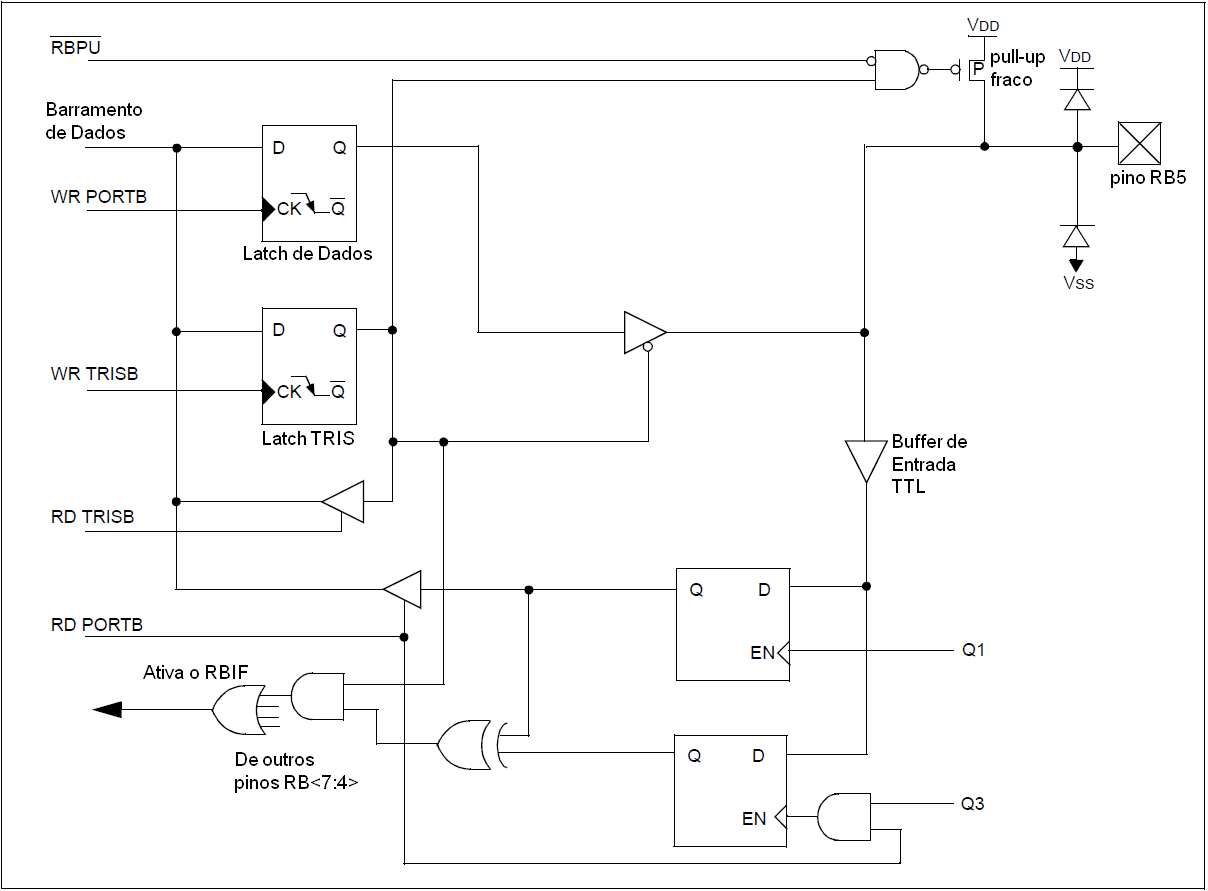

FIGURA 5.13: DIAGRAMA DE BLOCOS DO PINO RB5

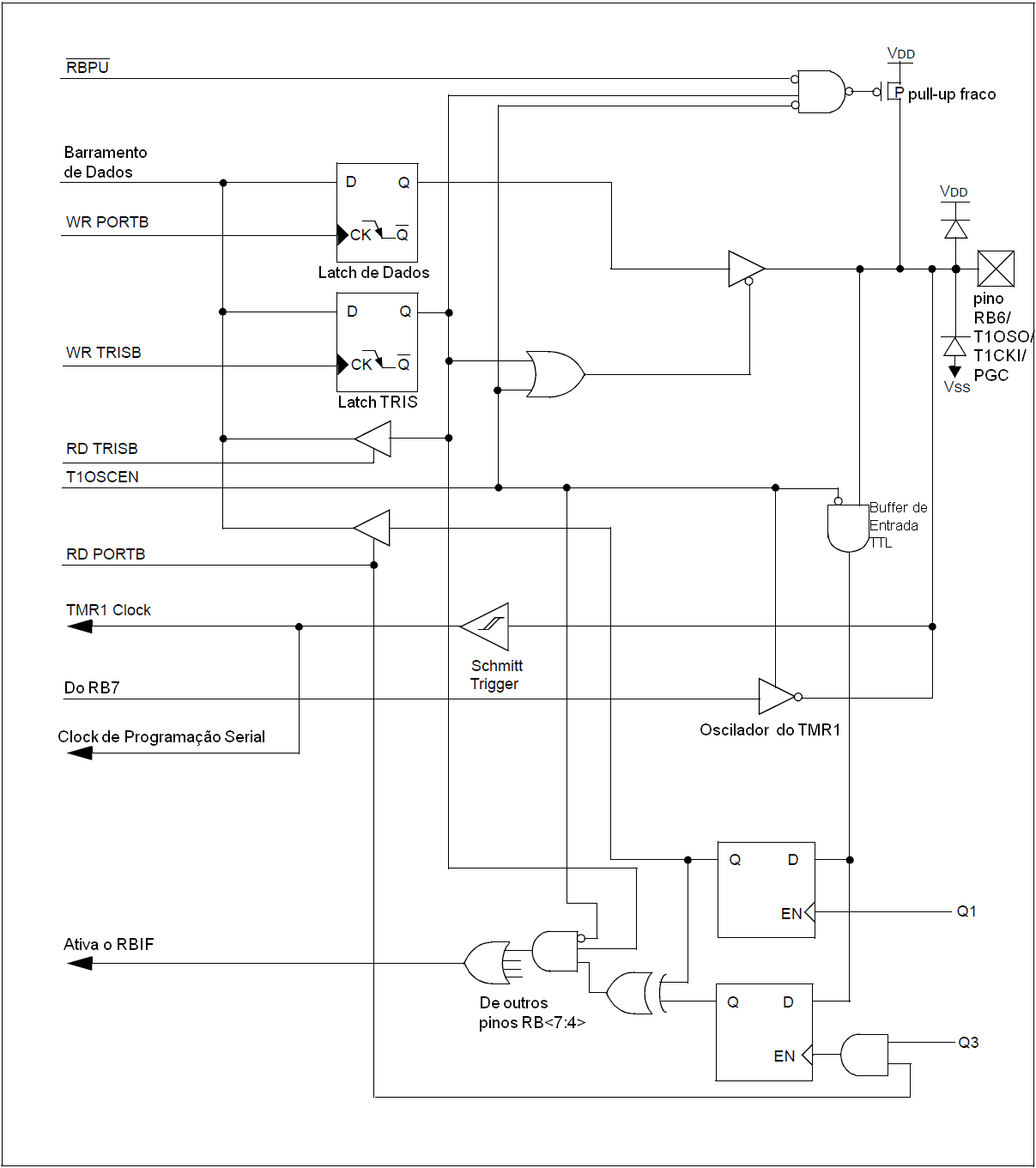

FIGURA 5.14: DIAGRAMA DE BLOCOS DO PINO RB6/T1OSO/T1CKI/PGC

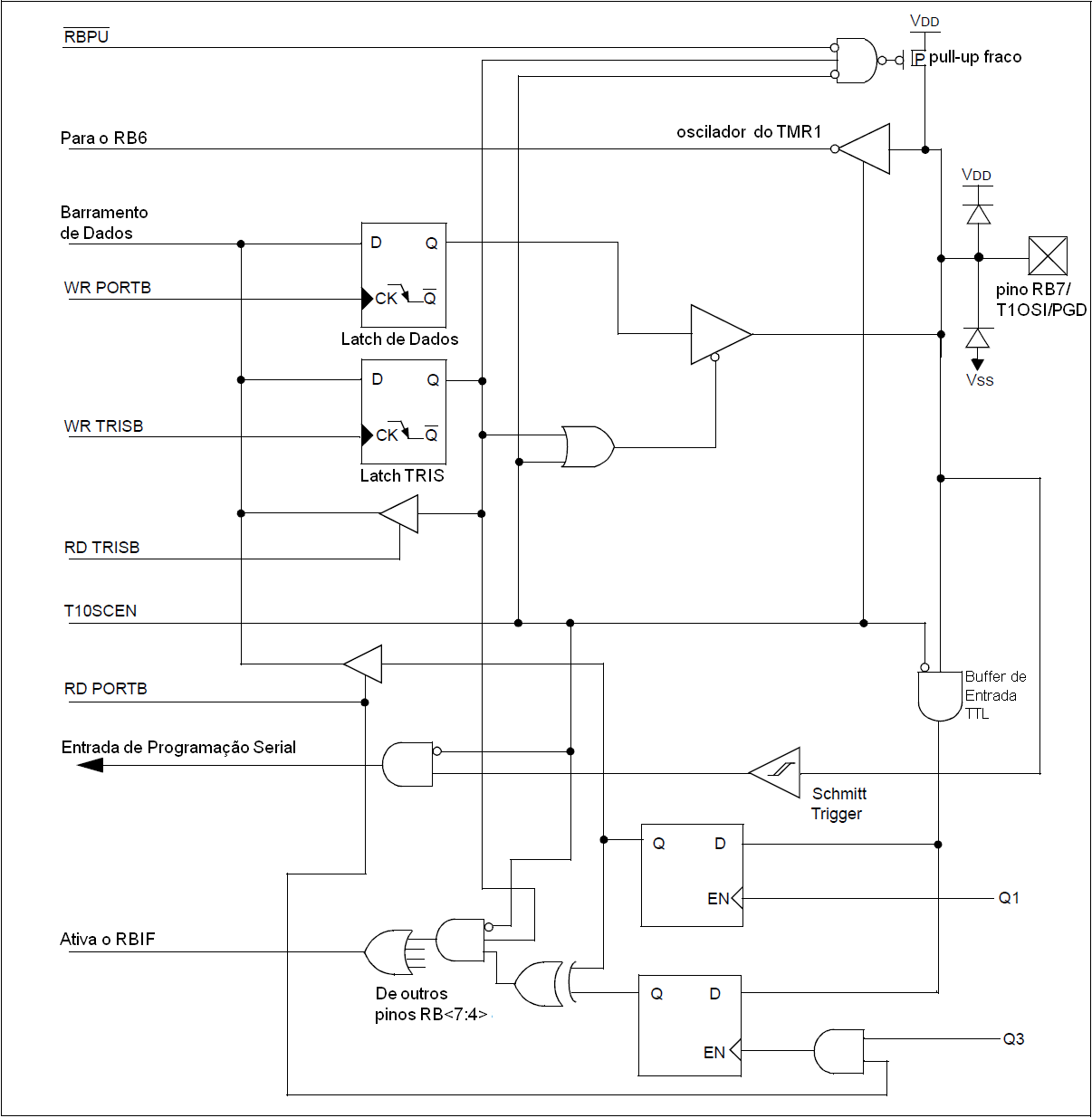

FIGURA 5.15: DIAGRAMA DE BLOCOS DO PINO RB7/T1OSI/PGD

|

Nome |

Função |

Tipo de Entrada |

Tipo de Saída |

Descrição |

|

RB0/INT |

RB0 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

INT |

ST |

--- |

Interrupção externa |

|

RB1/RX/DT |

RB1 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

RX |

ST |

--- |

Pino de recepção USART |

|

DT |

ST |

CMOS |

Entrada/ saída de dados sincronizada |

|

RB2/TX/CK |

RB2 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. |

|

TX |

--- |

CMOS |

Pino de transmissão USART |

|

CK |

ST |

CMOS |

Entrada/ saída de clock sincronizada. Pode ser programada por software para pull-up interno fraco. |

|

RB3/CCP1 |

RB3 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

CCP1 |

ST |

CMOS |

Entrada e Saída do tipo Captura/Comparação/PWM |

|

RB4/PGM |

RB4 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Interrupção por alteração no pino. Pode ser programada por software para pull-up interno fraco. |

|

PGM |

ST |

--- |

Pino de entrada de programação em baixa voltagem. Quando a programação em baixa voltagem está habilitada, a interrupção por alteração no pino, bem como o resistor de pull-up fraco, estão desabilitados. |

|

RB5 |

RB5 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Interrupção por alteração no pino. Pode ser programada por software para pull-up interno fraco. |

|

RB6/T1OSO/T1CKI/PGC |

RB6 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Interrupção por alteração no pino. Pode ser programada por software para pull-up interno fraco. |

|

T1OSO |

--- |

XTAL |

Saída do oscilador do Timer1 |

|

T1CKI |

ST |

--- |

Entrada de clock do Timer1 |

|

PCG |

ST |

--- |

Clock de programação ICSPTM |

|

RB7/T1OSI/PGD |

RB7 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Interrupção por alteração no pino. Pode ser programada por software para pull-up interno fraco. |

|

T1OSI |

XTAL |

--- |

Entrada do oscilador do Timer1 |

|

PGD |

ST |

CMOS |

Entrada e saída de dados ICSP |

Legenda:

O = Saída (output)

CMOS = Saída CMOS

P = Energia (power)

--- = não utilizado(a)

I = Entrada (input)

ST = Entrada tipo Schmitt Trigger

TTL = Entrada TTL

OD = Saída de dreno aberto (open drain)

AN = analógico(a)

TABELA 5.4: RESUMO DOS REGISTRADORES ASSOCIADOS À PORTB

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

06h, 106h |

PORTB |

RB7 |

RB6 |

RB5 |

RB4(1) |

RB3 |

RB2 |

RB1 |

RB0 |

xxxx xxxx |

uuuu uuuu |

|

86h, 186h |

TRISB |

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

1111 1111 |

1111 1111 |

|

81h, 181h |

OPTION |

RBPU |

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

1111 1111 |

1111 1111 |

Legenda:

u = inalterado

x = desconhecido

células sombreadas = não utilizadas para a PORTB

Nota 1: O bit de configuração LVP ativa a funcionalidade do RB4.

5.3.1 PORTAS I/O BIDIRECIONAIS

Qualquer instrução de escrita opera internamente como uma operação de leitura seguida por uma operação de escrita. As instruções BCF e BSF, por exemplo, leem o registrador na CPU, executam a operação no bit e escrevem o resultado de volta no registrador. Deve-se tomar cuidado ao se aplicar estas instruções em uma porta com entradas e saídas definidas sumultaneamente. Por exemplo, uma operação BSF no bit 5 da PORTB implicará na leitura de todos os 8 bits da PORTB na CPU. Então a operação BSF ocorre no bit 5 e a PORTB é escrita nas latches de saída. Se um outro bit da PORTB é utilizado como um pino I/O bidirecional (p. ex. o bit 0) e é definido como entrada neste momento, o sinal de entrada presente no pino propriamente dito será lido na CPU e reescrito na latch de dados deste pino em particular, sobrescrevendo o conteúdo anterior. Enquanto o pino permanece no modo de Entrada, não ocorre nenhum problema. Entretanto, se mais tarde o bit 0 é alterado para o modo de Saída, o conteúdo da latch de dados pode ser agora desconhecido.

A leitura de um registrador de porta detecta os valores dos pinos da porta. A escrita no registrador de porta grava o valor na latch da porta. Quando se utiliza as instruções do tipo ler-modificar-escrever (p. ex. BCF, BSF, etc.) em uma porta, o valor dos pinos da porta é lido, a operação desejada é executada com este valor, e este valor é escrito na latch da porta.

O Exemplo 5.2 mostra o efeito de duas instruções sequenciais do tipo ler-modificar-escrever (p. ex. BCF, BSF, etc.) em uma porta I/O.

Um pino produzindo ativamente saídas Alto ou Baixo não deve concomitantemente receber comandos de dispositivos externos a fim de ter o seu nível alterado ("wired-OR", "wired-AND"). As altas correntes de saída resultantes podem danificar o chip.

;Configurações iniciais da porta: PORTB<7:4> entradas

; PORTB<3:0> saídas

;PORTB<7:6> possuem pull-up externos e não são

;conectados a outros circuitos

;PORT latch PORT Pins

;---------- ----------

BCF STATUS, RP0 ;

BCF PORTB, 7 ;01pp pppp 11pp pppp

BSF STATUS, RP0 ;

BCF TRISB, 7 ;10pp pppp 11pp pppp

BCF TRISB, 6 ;10pp pppp 10pp pppp

;Note que o usuário provavelmente esperava que os

;os valores nos pinos fossem 00pp pppp. A segunda

;instrução BCF causou o armazenamento de RB7 como valor

;do pino (alto)

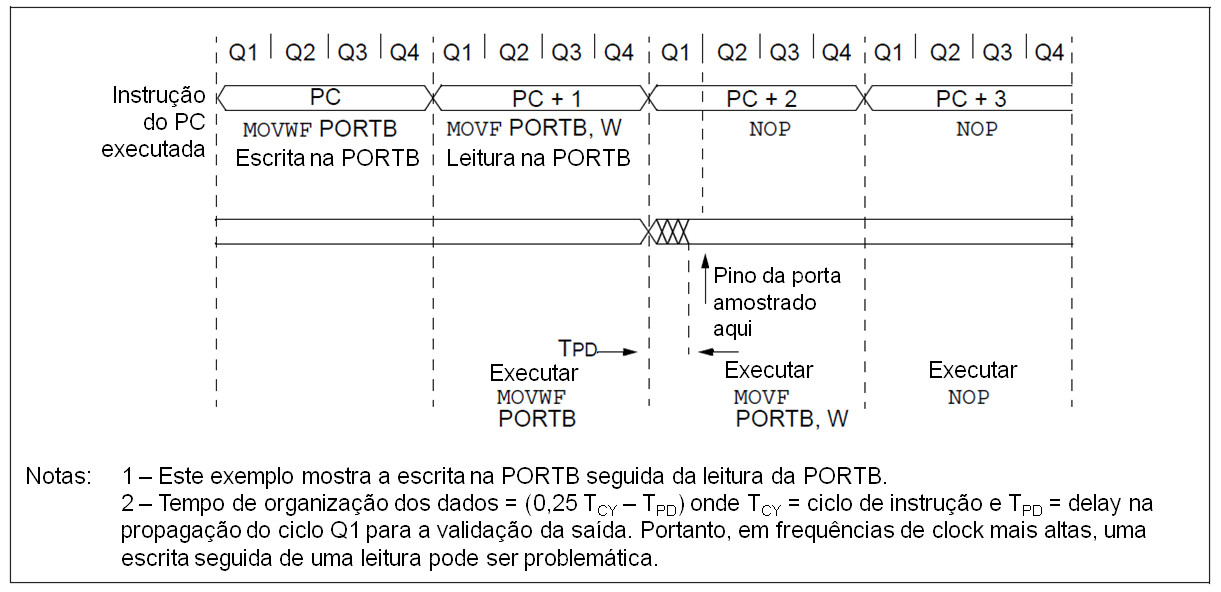

5.3.2 OPERAÇÕES SUCESSIVAS EM PORTAS I/O

A efetivação da escrita em uma porta I/O ocorre no final de um ciclo de instrução, ao passo que, para a leitura, os dados devem ser validados no início do ciclo de instrução (Figura 5.16). Portanto, deve-se tomar cuidado se uma operação de escrita seguida de uma operação de leitura é executada na mesma porta I/O. A sequência de instruções deve ser tal que permita a estabilização da voltagem do pino (dependente da carga) antes que próxima instrução, que causa a leitura daquele registro na CPU, seja executada. Caso contrário, o estado anterior do pino pode ser lido na CPU, ao invés do estado atual. Em caso de dúvida, é melhor separar estas instruções com uma NOP, ou uma outra instrução que não acesse esta porta I/O.