Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

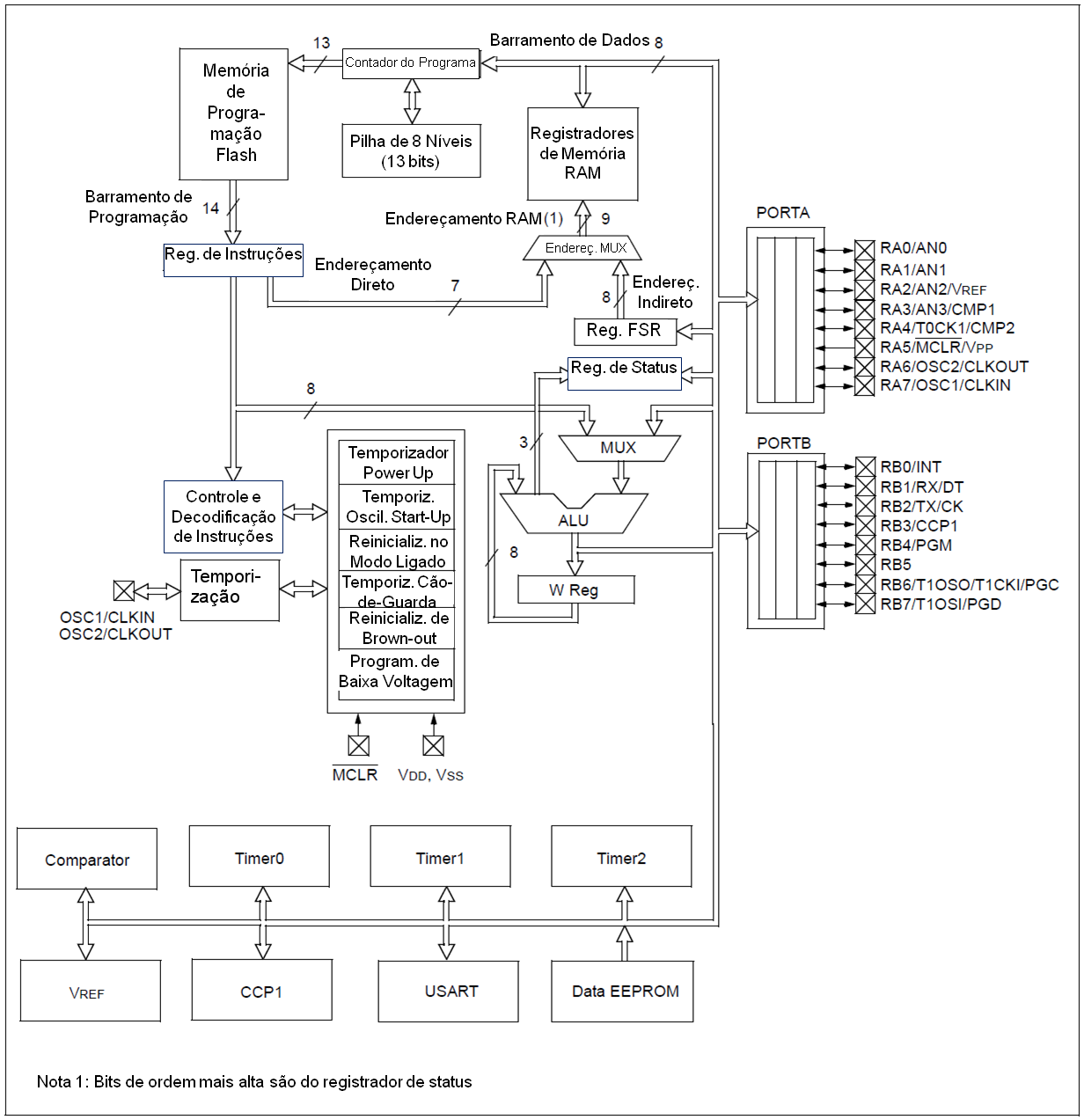

A alta performance da família de microcontroladores PIC16F627A, PIC16F628A e PIC16F648A pode ser atribuída a uma série de características de arquitetura comumente encontradas em microprocessadores RISC. Um primeiro fator é o de que os PIC16F627A/628A/648A utilizam a arquitetura Harvard, na qual o programa e os dados são acessados em memórias separadas, utilizando barramentos separados. Isso melhora a largura da banda, em comparação com a arquitetura tradicional Von Neumann, na qual o programa e os dados são acessados em uma mesma memória. A separação das memórias de programa e de dados permite ainda que as instruções sejam dimensionadas em palavras com largura diferente de 8 bits. Os códigos operacionais das instruções possuem largura de 14 bits, tornando possível que todas as instruções sejam constituidas de apenas uma única palavra. Um barramento de acesso à memória de programa com 14 bits de largura busca uma instrução de 14 bits em um ciclo único. Um pipeline de dois estágios sobrepõe a busca e a execução das instruções. Consequentemente, todas as instruções (35) são executadas em um único ciclo (200ns @ 20 MHz), exceto para desvio na execução do programa.

A Tabela 3.1 lista os tamanhos das memórias dos componentes (Memórias Flash, de dados e EEPROM).

|

Componente |

Memória |

|

Memória de Programação Flash |

Memória de Dados RAM |

Memória de Dados EEPROM |

|

PIC16F627A |

1024 x 14 |

224 x 8 |

128 x 8 |

|

PIC16F628A |

2048 x 14 |

224 x 8 |

128 x 8 |

|

PIC16F648A |

4096 x 14 |

256 x 8 |

256 x 8 |

|

PIC16LF627A |

1024 x 14 |

224 x 8 |

128 x 8 |

|

PIC16LF628A |

2048 x 14 |

224 x 8 |

128 x 8 |

|

PIC16LF648A |

4096 x 14 |

256 x 8 |

256 x 8 |

Os PIC16F627A/628A/648A podem endereçar direta ou indiretamente seus bancos de registradores ou memória de dados. Todos os Registradores de Funções Especiais (Special Function Registers - SFR), incluindo o contador do programa, estão mapeados na memória de dados. Os PIC16F627A/628A/648A possuem um conjunto de instruções ortogonal (simétrico) que torna possível carregar qualquer operação, em qualquer registrador de memória, utilizando qualquer modo de endereçamento. Esta natureza simétrica e falta de 'situações ótimas especiais' torna a programação com os PIC16F627A/628A/648A simples, porém eficiente. Além disso, a curva de aprendizado é significativamente reduzida.

Os componentes PIC16F627A/628A/648A contêm uma Unidade Lógica Aritmética (ALU) e um registrador de trabalho de 8 bits. A ALU é uma unidade aritmética de propósito genérico. Ela executa operações aritméticas e booleanas entre os dados no registrador de trabalho e qualquer outro registrador de memória.

A ALU tem 8 bits de largura e tem capacidade de executar operações de adição, subtração, deslocamento, bem como operações lógicas. Salvo indicação em contrário, as operações aritméticas são feitas em complemento de dois. Em instruções de dois operandos, um deles é tipicamente o registrador de trabalho (W-register). O outro operando é um registrador de memória ou uma constante imediata. Em instruções de operando único, o operando é o W-register ou um registrador de memória.

Dependendo da instrução executada, a ALU pode afetar os valores dos bits Carry (C), Digit Carry (DC) e Zero (Z) no registrador de status. os bits C e DC operam como bits de empréstimo (Borrow) e de empréstimo de dígito (Digit Borrow), respectivamente, na subtração. Veja as instruções SUBLW e SUBWF como exemplos.

Um diagrama de blocos simplificado é apresentado na Figura 3.1, e uma descrição dos pinos do componente é mostrada na Tabela 3.2.

Dois tipos de memória de dados são fornecidos nos componentes PIC16F627A/628A/648A. A memória de dados não-volátil EEPROM é oferecida para armazenamento de dados por longos períodos, como por exemplo valores de calibração, dados de tabelas de consulta, ou quaisquer outros dados que podem requerer uma atualização periódica no campo. Estes tipos de dados não são perdidos quando a energia é interrompida. A outra memória de dados fornecida é a memória de dados regular RAM. A memória de dados regular RAM é oferecida para o armazenamento temporário de dados durante a operação normal. Os dados são perdidos quando a energia é desligada.

|

Nome |

Função |

Tipo de Entrada |

Tipo de Saída |

Descrição |

|

RA0/AN0 |

RA0 |

ST |

CMOS |

Porta de entrada/ saída bidirecional |

|

AN0 |

AN |

--- |

Entrada do comparador analógico |

|

RA1/AN1 |

RA1 |

ST |

CMOS |

Porta de entrada/ saída bidirecional |

|

AN1 |

AN |

--- |

Entrada do comparador analógico |

|

RA2/AN2/VREF |

RA2 |

ST |

CMOS |

Porta de entrada/ saída bidirecional |

|

AN2 |

AN |

--- |

Entrada do comparador analógico |

|

VREF |

--- |

AN |

Saída da VREF |

|

RA3/AN3/CMP1 |

RA3 |

ST |

CMOS |

Porta de entrada/ saída bidirecional |

|

AN3 |

AN |

--- |

Entrada do comparador analógico |

|

CMP1 |

--- |

CMOS |

Saída do comparador 1 |

|

RA4/T0CKI/CMP2 |

RA4 |

ST |

OD |

Porta de entrada/ saída bidirecional |

|

T0CKI |

ST |

--- |

Entrada de clock do Timer0 |

|

CMP2 |

--- |

OD |

Saída do comparador 2 |

|

RA5/MCLR/VPP |

RA5 |

ST |

--- |

Porta de entrada |

|

MCLR |

ST |

--- |

Reset principal. Quando configurado como MCLR, este pino representa uma reinicialização do dispositivo. ativa em nível baixo. A tensão no MCLR/VPP não pode exceder a VDD durante a operação normal do dispositivo. |

|

VPP |

--- |

--- |

Entrada de tensão de programação |

|

RA6/OSC2/CLKOUT |

RA6 |

ST |

CMOS |

Porta de entrada/saída bidirecional |

|

OSC2 |

--- |

XTAL |

Saída do oscilador de cristal. Se conecta com o ressonador a cristal no modo Oscilador de Cristal |

|

CLKOUT |

--- |

CMOS |

No modo RC ou INTOSC. O pino OSC2 pode ser a saída CLKOUT, o qual tem 1/4 da frequência do OSC1 |

|

RA7/OSC1/CLKIN |

RA7 |

ST |

CMOS |

Porta de entrada/saída bidirecional |

|

OSC1 |

XTAL |

--- |

Entrada do oscilador de cristal |

|

CLKIN |

ST |

--- |

Entrada da fonte de clock externa. Pino de polarização RC. |

|

RB0/INT |

RB0 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

INT |

ST |

--- |

Interrupção externa |

|

RB1/RX/DT |

RB1 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

RX |

ST |

--- |

Pino de recepção USART |

|

DT |

ST |

CMOS |

Entrada/saída de dados sincronizada |

|

RB2/TX/CK |

RB2 |

TTL |

CMOS |

Porta de entrada/ saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

TX |

--- |

CMOS |

Pino de transmissão USART |

|

CK |

ST |

CMOS |

Entrada/saída de clock sincronizada. |

|

RB3/CCP1 |

RB3 |

TTL |

CMOS |

Porta de entrada/saída bidirecional. Pode ser programada por software para pull-up interno fraco. |

|

CCP1 |

ST |

CMOS |

Entrada e Saída do tipo Captura/Comparação/PWM |

|

RB4/PGM |

RB4 |

TTL |

CMOS |

Porta de entrada/saída bidirecional. Alteração de interrupção no pino. Pode ser programada por software para pull-up interno fraco. |

|

PGM |

ST |

--- |

Pino de entrada de programação em baixa tensão. Quando a programação em baixa tensão está habilitada, a alteração de interrupção no pino, bem como o resistor de pull-up fraco, estão desabilitados. |

|

RB5 |

RB5 |

TTL |

CMOS |

Porta de entrada/saída bidirecional. Alteração de interrupção no pino. Pode ser programada por software para pull-up interno fraco. |

|

RB6/T1OSO/T1CKI/PGC |

RB6 |

TTL |

CMOS |

Porta de entrada/saída bidirecional. Alteração de interrupção no pino. Pode ser programada por software para pull-up interno fraco. |

|

T1OSO |

--- |

XTAL |

Saída do oscilador do Timer1 |

|

T1CKI |

ST |

--- |

Entrada de clock do Timer1 |

|

PCG |

ST |

--- |

Clock de programação ICSPTM |

|

RB7/T1OSI/PGD |

RB7 |

TTL |

CMOS |

Porta de entrada/saída bidirecional. Alteração de interrupção no pino. Pode ser programada por software para pull-up interno fraco. |

|

T1OSI |

XTAL |

--- |

Entrada do oscilador do Timer1 |

|

PGD |

ST |

CMOS |

Entrada e saída de dados ICSP |

|

VSS |

VSS |

Energia |

--- |

Referência de TERRA para os pinos de lógica e de entrada/saída |

|

VDD |

VDD |

Energia |

--- |

Pino de alimentação positiva para os pinos de lógica e entrada/saída |

Legenda:

O = Saída (output)

CMOS = Saída CMOS

P = Energia (power)

--- = não utilizado(a)

I = Entrada (input)

ST = Entrada tipo Schmitt Trigger

TTL = Entrada TTL

OD = Saída de dreno aberto (open drain)

AN = analógico(a)

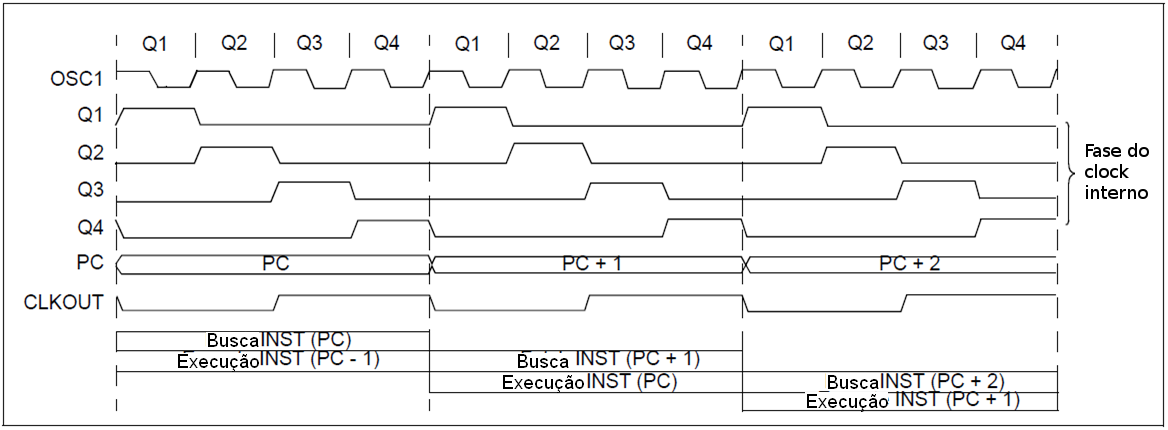

A entrada de clock (pino RA7/OSC1/CLKIN) é internamente dividida por quatro, de forma a gerar quatro clocks em quadratura não sobrepostos, a saber Q1, Q2, Q3 e Q4. Internamente, o contador de programa (PC) é incrementado a cada Q1, a instrução é buscada na memória de programa e guardada no registrador de instruções em Q4. A instrução é decodificada e executada durante os ciclos Q1 a Q4 seguintes. Os clocks e o fluxo de execução da instrução são apresentados na Figura 3.2.

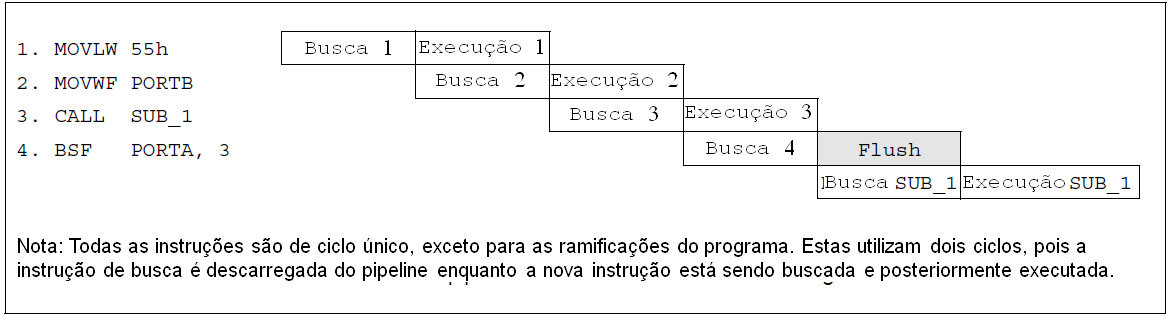

3.2 Fluxo de Instrução/Canalização (pipelining)

Um ciclo de instrução consiste em quatro ciclos Q (Q1, Q2, Q3 e Q4). A busca e a execução da instrução são canalizadas de forma que a busca utilize um ciclo de instrução, enquanto a decodificação e a execução utilizem um outro ciclo de instrução. Entretanto, devido à canalização, cada instrução é efetivamente executada em um ciclo. Se uma instrução causa uma alteração no contador do programa (p. ex. GOTO), então dois ciclos são necessários para completar a instrução (Exemplo 3.1)

Um ciclo de busca começa com o incremento do contador de programa em Q1.

No ciclo de execução, a instrução buscada é guardada no Registrador de Instruções (IR) no ciclo Q1. Esta instrução é então decodificada e executada durante os ciclos Q2, Q3 e Q4. A memória de dados é lida durante o Q2 (leitura do operando) e escrita durante o Q4 (escrita no destino).