Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

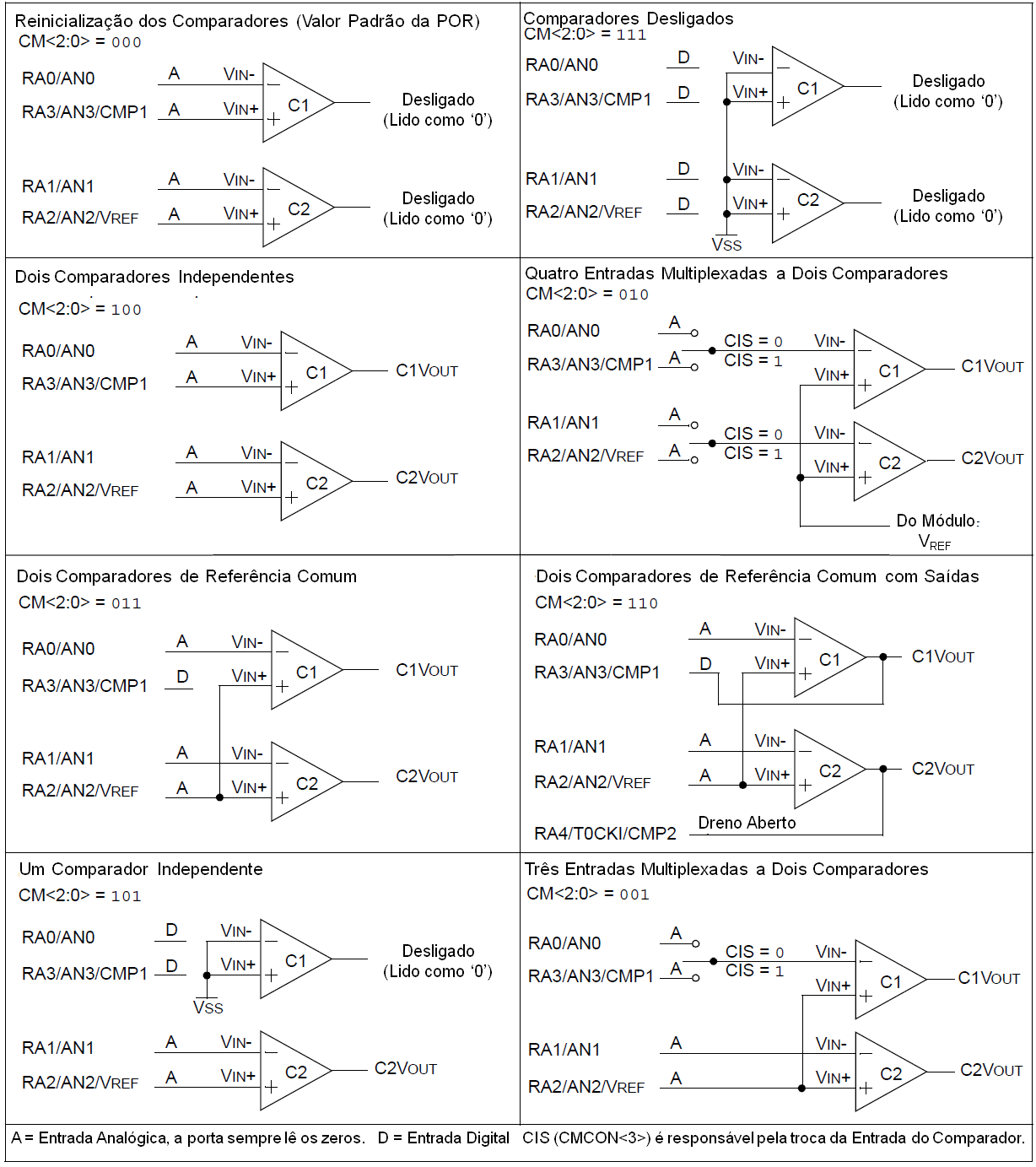

O módulo comparador dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A contem dois comparadores analógicos. As entradas para os comparadores são multiplexadas com os pinos RA0 até RA3. A Referência de Tensão on-chip (no chip) (Seção 11.0 "Módulo de Referência de Tensão") também pode ser uma entrada para os comparadores.

O registrador CMCON, apresentado no Registrador 10.1, controla os multiplexadores de entrada e saída do comparador. Um diagrama de blocos do comparador é apresentado na Figura 10.1.

|

|

|

R-0 |

R-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

|

C2OUT |

C1OUT |

C2INV |

C1INV |

CIS |

CM2 |

CM1 |

CM0 |

|

bit 7 |

|

|

|

|

|

|

bit 0 |

|

|

bit 7 |

C2OUT: Bit de Saída do Comparador 2 |

|

|

Quando C2INV = 0 |

|

|

1 = C2 VIN+ > C2 VIN- |

|

|

0 = C2 VIN+ < C2 VIN- |

|

|

Quando C2INV = 1 |

|

|

1 = C2 VIN+ < C2 VIN- |

|

|

0 = C2 VIN+ > C2 VIN-

|

|

bit 6 |

C1OUT: Bit de Saída do Comparador 1 |

|

|

Quando C1INV = 0 |

|

|

1 = C1 VIN+ > C1 VIN- |

|

|

0 = C1 VIN+ < C1 VIN- |

|

|

Quando C1INV = 1 |

|

|

1 = C1 VIN+ < C1 VIN- |

|

|

0 = C1 VIN+ > C1 VIN-

|

|

bit 5 |

C2INV: Bit de Inversão da Saída do Comparador 2 |

|

|

1 = Saída do C2 invertida |

|

|

0 = Saída do C2 não-invertida

|

|

bit 4 |

C1INV: Bit de Inversão da Saída do Comparador 1 |

|

|

1 = Saída do C1 invertida |

|

|

0 = Saída do C1 não-invertida

|

|

bit 3 |

CIS: Bit de Troca da Entrada do Comparador |

|

|

Quando CM<2:0> = 001 |

|

|

Então: |

|

|

1 = C1 VIN- se conecta ao RA3 |

|

|

0 = C1 VIN- se conecta ao RA0 |

|

|

Quando CM<2:0> = 010 |

|

|

Então: |

|

|

1 = C1 VIN- se conecta ao RA3

e C2 VIN- se conecta ao RA2 |

|

|

0 = C1 VIN- se conecta ao RA0

e C2 VIN- se conecta ao RA1

|

|

bit 2-0 |

CM<2:0>: Bits do Modo do Comparador |

|

|

A Figura 10.1 apresenta os modos comparadores e as configurações dos bits CM<2:0>

|

|

|

Legenda:

R = bit de leitura

W = bit de escrita

U = bit não implementado (unimplemented), lido como '0'

-n = valor na POR

'1' = bit está ativado

'0' = bit está apagado

x = bit é desconhecido |

10.1 Configuração do Comparador

Existem oito modos de comparação para os comparadores. O registrador CMCON é utilizado para selecionar o modo. A Figura 10.1 apresenta os oito modos possíveis. O registrador TRISA controla o direcionamento de dados dos pinos do comparador para cada modo.

Se o modo do Comparador é alterado, o nível de saída do comparador pode não ser válido para o delay da alteração de modo especificada, apresentado na Tabela 17.2.

Nota 1:

As interrupções do Comparador devem estar desabilitadas durante uma alteração de modo do Comparador, caso contrário pode ocorrer uma falsa interrupção.

Nota 2:

Comparadores podem possuir uma saída invertida. Veja a

Figura 10.1.

O exemplo de código no Exemplo 10.1 descreve os passos necessários para configurar o módulo Comparador. O RA3 e o RA4 são configurados como saída digital. O RA0 e o RA1 são configurados como as entradas V-, e o RA2 como a entrada V+ para ambos os comparadores.

FLAG_REG EQU 0X20

CLRF FLAG_REG ;Inicializa o registrador de flags

CLRF PORTA ;Inicializa PORTA

MOVF CMCON, W ;Carrega os bits do comparador

ANDLW 0xC0 ;Mascara os bits do comparador

IORWF FLAG_REG,F ;Armazena os bits no registrador de flags

MOVLW 0x03 ;Inicializa o modo do comparador

MOVWF CMCON ;CM<2:0> = 011

BSF STATUS,RP0 ;Seleciona o Banco 1

MOVLW 0x07 ;Inicializa a direção dos dados

MOVWF TRISA ;Configura RA<2:0> como entrada

;e RA<4:3> como saídas

;TRISA<7:5> é sempre lido como '0'

BCF STATUS,RP0 ;Seleciona o Banco 0

CALL DELAY10 ;Delay de 10ms

MOVF CMCON,F ;Lê CMCON para finalizar a

;alteração de condição

BCF PIR1,CMIF ;Apaga interrupções pendentes

BSF STATUS,RP0 ;Seleciona o Banco 1

BSF PIE1,CMIE ;Habilita as inter do comparador

BCF STATUS,RP0 ;Seleciona o Banco 0

BSF INTCON,PEIE ;Habilita as interrupções dos periféricos

BSF INTCON,GIE ;Habilita interrupções globais

10.2 Operação do Comparador

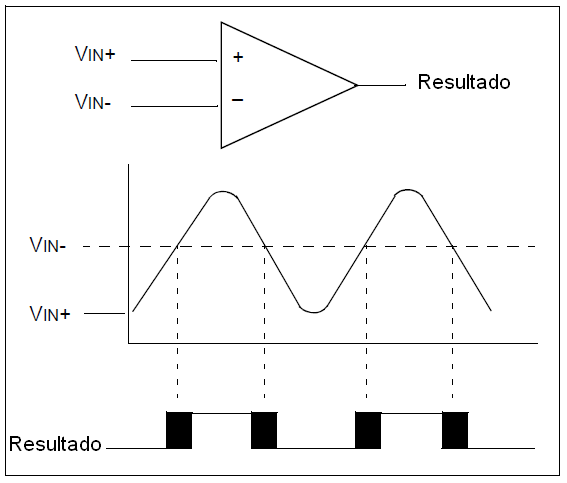

Um comparador simples é apresentado na Figura 10.2 juntamente com a relação entre os níveis de entrada analógica e a saída digital. Quando a entrada analógica na VIN+ é menor que a entrada analógica VIN-, a saída do comparador é um nível digital baixo. Quando a entrada analógica na VIN+ é maior que a entrada analógica VIN-, a saída do comparador é um nível digital alto. As áreas sombreadas da saída do comparador na Figura 10.2 representam a incerteza devido aos offsets (diferenças de valor) de entrada e ao tempo de resposta. Veja a Tabela 17.2 para a voltagem do Modo Comum.

10.3 Referência do Comparador

Um sinal de referência externo ou interno pode ser utilizado dependendo do modo de Operação do comparador. O sinal analógico que está presente na VIN- é comparado com o sinal na VIN+, e a saída digital do comparador é adequadamente ajustada(Figura 10.2).

10.3.1 SINAL DE REFERÊNCIA EXTERNO

Quando referências de tensão externas são utilizadas, o módulo Comparador pode ser configurado para que os comparadores operem a partir da mesma fonte de referência, ou de fontes diferentes. Entretanto, aplicações de detecção de limites podem requerer uma mesma referência. O sinal de referência deve estar entre VSS e VDD, e pode ser aplicado a qualquer pino do(s) comparador(es).

10.3.2 SINAL DE REFERÊNCIA INTERNO

O módulo Comparador também permite a seleção de uma referência de tensão gerada internamente para os comparadores. A Seção 11.0 "Módulo de Referência de Tensão" contém uma descrição detalhada do módulo de Referência de Tensão que provê este sinal. O sinal de referência interno é utilizado quando os comparadores estão no modo CM<2:0>=010 (Figura 10.1). Neste modo, a referência interna de tensão é aplicada ao pino VIN+ de ambos os comparadores.

10.4 Tempo de Resposta do Comparador

O tempo de resposta é o tempo mínimo, após a seleção de uma nova tensão de referência ou fonte de entrada, até que a saída do comparador tenha um nível válido. Se a referência interna é alterada, o máximo delay da referência interna de tensão deve ser considerado ao se utilizar as saídas do comparador. Caso contrário, o máximo delay dos comparadores deve ser utilizado (Tabela 17.2).

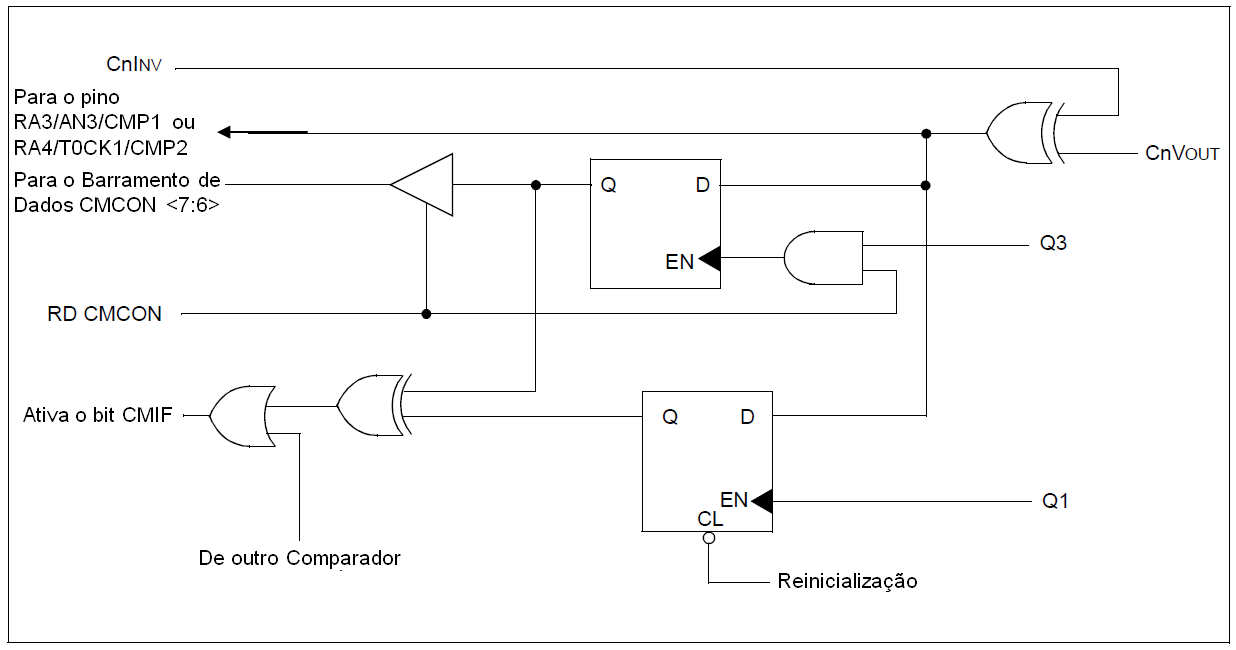

10.5 Saídas do Comparador

As saídas do comparador são lidas através do registrador CMCON. Estes bits são acessíveis somente para leitura. As saídas do comparador podem também ser diretamente enviadas para os pinos I/O RA3 e RA4. Quando o CM<2:0>=110 ou 001, multiplexadores no caminho de saída dos pinos RA3 e RA4/T0CKI/CMP2 serão acionados e a saída de cada pino será a saída não-sincronizada do comparador. A incerteza de cada um dos comparadores está relacionada à tensão de offset de entrada e ao tempo de resposta dado nas especificações. A Figura 10.3 apresenta o diagrama de blocos da saída do comparador.

Os bits TRISA ainda funcionarão para habilitar/ desabilitar a saída para oa pinos RA3/AN3/CMP1 e RA4/T0CKI/CMP2, enquanto estiverem neste modo.

Nota 1:

Durante a leitura do registrador PORT, todos os pinos configurados como entradas analógicas serão lidos como '0'. Os pinos configurados como entradas digitais converterão uma entrada analógica, de acordo com a especificação da entrada de Schmitt Trigger.

Nota 2:

Níveis analógicos em qualquer pino que estiver definido como entrada digital podem fazer o buffer de entrada consumir mais energia do que a especificada.

O sinalizador de interrupção do comparador é ativado sempre que ocorrer uma alteração no valor da saída de qualquer comparador. Será necessário que o software mantenha as informações sobre o status dos bits de saída, lidos no CMCON<7:6>, a fim de determinar a alteração mais recentemente ocorrida. O bit CMIF, PIR <6>, é o sinalizador de interrupção do comparador. O CMIF deve ser reinicializado apagando-se com o valor '0'. Como também é possível se escrever um '1' no registrador, uma interrupção simulada pode ser inciada.

O bit CMIE (PIE<6>) e o bit PEIE (INTCON<6>) devem ser ativados para habilitar a interrupção. Além disso, o bit GIE também deve ser ativado. Se qualquer destes bits for apagado, a interrupção não é habilitada, embora o bit CMIF ainda seja ativado se ocorrer uma condição de interrupção.

Nota:

Caso ocorra uma alteração no registrador CMCON (C1OUT ou C2OUT) enquanto uma operação de leitura estiver sendo executada (início do ciclo Q2), o sinalizador de interrupção CMIF (PIR<6>) pode não ser ativado.

O usuário pode, durante a rotina de serviço de interrupção, apagar a interrupção da seguinte maneira:

-

Executando qualquer escrita ou leitura do CMCON. Isto encerrará a condição de não-equivalência (mismatch)

-

Apagando o bit sinalizador CMIF

A condição de mismatch continuará a ativar o bit CMIF. A leitura do CMCON encerrará a condição de mismatch e permitirá que o bit CMIF seja apagado.

10.7 Operação do Comparador durante a Hibernação

Quando um comparador está ativo e o equipamento está no modo de Hibernação, o comparador permanece ativo e a interrupção é funcional caso seja habilitada. Esta interrupção removerá o equipamento do modo de Hibernação quando for habilitada. Enquando o comparador é ativado, a corrente atingirá valores maiores do que o baixo valor de corrente especificado para a Hibernação. Cada comparador que esteja em operação consumirá uma energia adicional, conforme apresentado nas especificações do comparador. Para minimizar o consumo de energia, durante o modo de Hibernação, desligue os comparadores, CM<2:0>=111, antes que o equipamento entre neste modo. Se o equipamento for removido da Hibernação, o conteúdo do registrador CMCON não é afetado.

10.8 Efeitos de uma Reinicialização

A Reinicialização do equipamento força o registrador CMCON para o seu estado de Reinicialização. Isto força o módulo Comparador a estar no modo de Reinicialização do comparador, CM<2:0<=000. Este fato garante que todas as potenciais entradas sejam analógicas. A corrente do dispositivo é minimizada quando entradas analógicas estão presentes no momento da reinicialização. Os comparadores serão desativados durante o intervalo de Reinicialização.

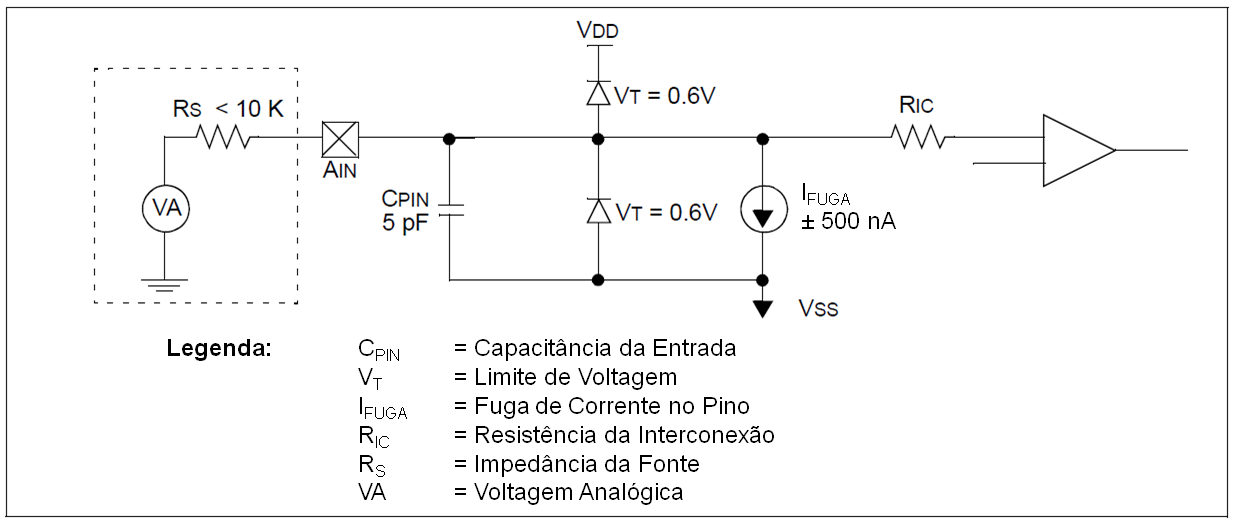

10.9 Considerações sobre a Conexão da Entrada Analógica

Um circuito simplificado para uma entrada analógica é apresentado na Figura 10.4. Como os pinos analógicos estão conectados a uma saída digital, eles possuem diodos polarizados reversos para a VDD e a VSS. Portanto, a entrada analógica deve estar entre VSS e VDD. Se a voltagem de entrada se desviar deste intervalo em mais do que 0,6 V, em qualquer direção, um dos diodos é ainda mais polarizado, e pode ocorrer um curto-circuito. Uma impedância máxima de 10 kΩ é recomendada para fontes analógicas. Qualquer componente externo conectado a um pino de entrada analógica, tal como um capacitor ou um diodo Zener, deve ter muito pouca fuga de corrente.

TABELA 10.1: REGISTRADORES ASSOCIADOS AO MÓDULO COMPARADOR

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

1Fh |

CMCON |

C2OUT |

C1OUT |

C2INV |

C1INV |

CIS |

CM2 |

CM1 |

CM0 |

0000 0000 |

0000 0000 |

|

0Bh, 8Bh, 10Bh, 18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

8Ch |

PIE1 |

EEIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

0000 -000 |

|

85h |

TRISA |

TRISA7 |

TRISA6 |

TRISA5 |

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

1111 1111 |

1111 1111 |

Legenda:

x = desconhecido

u = inalterado

- = não implementado, lido como '0'