Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

O módulo temporizador/contador Timer0 dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possui as seguintes características:

-

Temporizador/contador de 8 bits

-

Capacidades de leitura e escrita

-

Pré-scaler de 8 bits programável por software

-

Seleção de clock interno ou externo

-

Interrupção no overflow de FFh a 00h

-

Seleção de borda para o clock externo

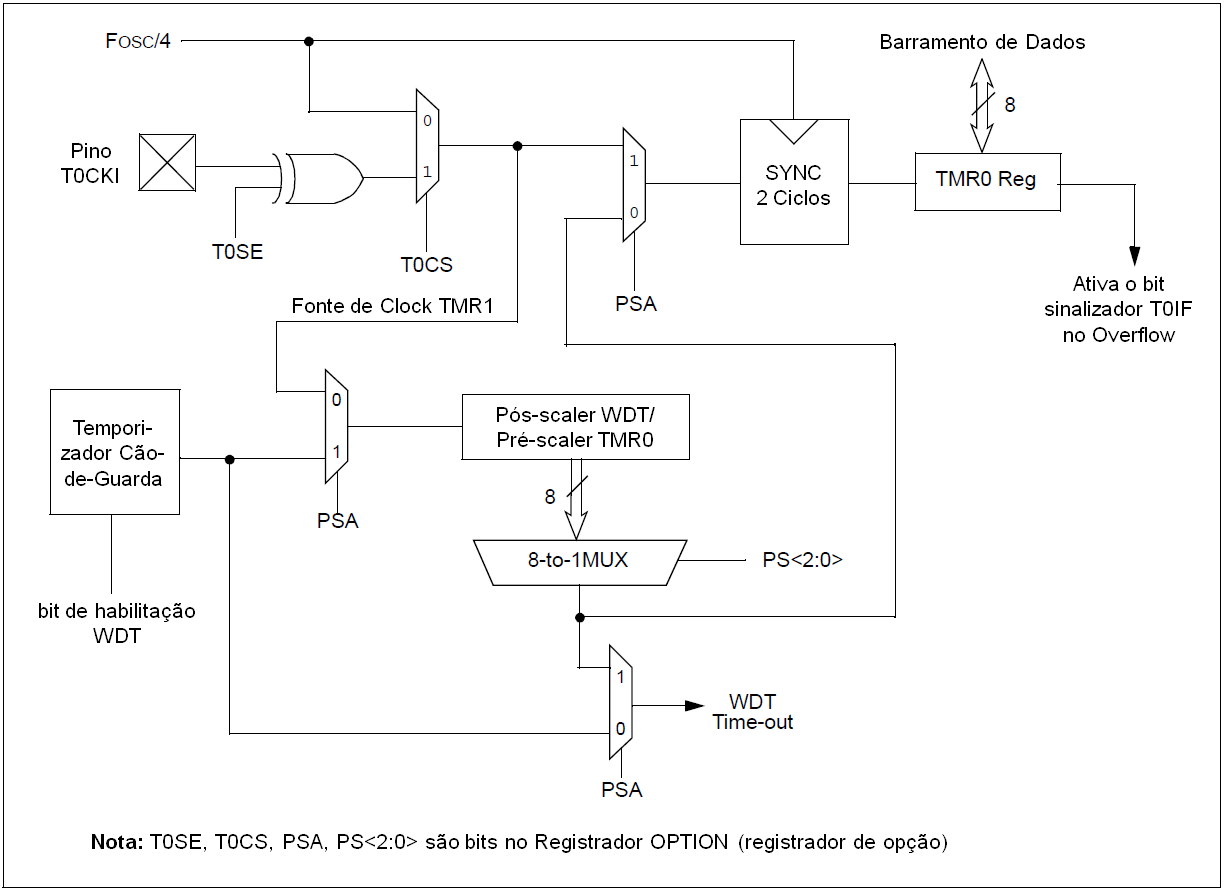

Na Figura 6.1 há um diagrama de blocos simplificado do módulo Timer0. Informações adicionais estão disponíveis no "Manual de Referência da Família de MCUs de Média Ordem PIC®" (DS33023).

O modo Timer é selecionado apagando-se o bit T0CS (OPTION<5>). No modo Timer, o valor do registrador TMR0 irá incrementar cada ciclo de instrução (sem pré-scaler). Se o registrador TMR0 é escrito, o incremento será inibido pelos próximos dois ciclos. O usuário pode contornar este fato escrevendo um valor inicial no registrador TMR0.

O modo Counter (contador) é selecionado ativando-se o bit T0CS. Neste modo, o valor do registrador TMR0 irá incrementar em cada borda de subida ou de descidado pino RA4/T0CKI/CMP2. A borda a incrementar é determinada pelo bit de controle da borda da fonte (T0SE) (OPTION<4>). Apagando-se o bit T0SE, a borda de subida é selecionada. Restrições na entrada do clock externo são discutidas na Seção 6.2 "Utilizando o Timer0 com Clock Externo".

O pré-scaler é dividido entre o módulo Timer0 e o Temporizador Cão-de-Guarda. A atribuição do pré-scaler é controlada pelo software através do bit de controle PSA (OPTION<3>). Apagando-se o bit PSA, o pré-scaler será atribuído ao Timer0. O pré-scaler não é acessível para leitura ou escrita. Quando o pré-scaler está atribuído ao módulo Timer0, o valor do pré-scaler pode ser selecionado dentre 1:2, 1:4, ..., 1:256. A Seção 6.3 "Pré-Scaler do Timer0" detalha a operação do pré-scaler.

6.1 Interrupção do Timer0

A interrupção do Timer0 é gerada quando o registrador temporizador/ contador TMR0 sofre overflow do FFh ao 00h. Este overflow ativa o bit T0IF. A interrupção pode ser mascarada apagando-se o bit T0IE (INTCON<5>). O bit T0IF (INTCON<2>) pode ser apagado pelo software através da rotina de serviço de interrupção do módulo Timer0, antes de reabilitar esta interrupção. A interrupção do Timer0 não pode acordar o processador da hibernação, pois o temporizador é desligado durante a hibernação.

Quando uma entrada de clock externo é utilizada para o Timer0, ela deve atender a certos requisitos. O requisito do clock externo se deve à sincronização do clock de fase interno (Tosc). Além disso, há um delay na incrementação atual do Timer0 depois da sincronização.

6.2.1 SINCRONIZAÇÃO DO CLOCK EXTERNO

Quando não é utilizado nenhum pré-scaler, a entrada do clock externo é a mesma que a saída do pré-scaler. A sincronização do T0CKI com o clock de fase interno é realizada amostrando-se a saída do pré-scaler nos ciclos Q2 e Q4 dos clocks de fase internos (Figura 6.1). Portanto, é necessário que o T0CKI esteja alto por pelo menos 2 Tosc (e um pequeno delay de 20ns do RC) e baixo por pelo menos 2 Tosc (e uma pequeno delay de 20ns do RC). Consulte a especificação elétrica do dispositivo desejado.

Quando um pré-scaler é utilizado, a entrada do clock externo é dividida pelo pré-scaler do tipo ripple-counter (contador-ripple ou contador por pulsação) assíncrono, de forma que a saída do pré-scaler seja simétrica. Para que o clock externo atenda ao requisito de amostragem, o contador-ripple deve ser levado em conta. Portanto, é necessário que o T0CKI tenha um período de pelo menos 4 Tosc (e um pequeno delay de 40ns do RC) dividido pelo valor do pré-scaler. O único requisito para os tempos do T0CKI alto e baixo é que eles não ultrapassem o limite mínimo de amplitude de pulsação de 10ns. Consulte os parâmetros 40, 42 e 42 na especificação elétrica do dispositivo desejado. Veja a Tabela 17.8.

Um contador de 8 bits está disponível como pré-scaler para o módulo Timer0, ou como pós-scaler para o Temporizador Cão-de-Guarda. A atribuição de pré-scaler para o módulo Timer0 implica em não haver pós-scaler para o Temporizador Cão-de-Guarda, e vice-versa.

Os bits PSA e PS<2:0> (OPTION<3:0>) determinam a atribuição do pré-scaler, bem como sua escala.

Quando atribuído ao módulo Timer0, todas as instruções escritas no registrador TMR0 (p. ex. CLRF 1, MONWF 1, BSF 1, x... etc.) apagarão o pré-scaler. Quando atribuído ao WDT (Watchdog Timer = Temporizador Cão-de-Guarda), uma instrução CLRWDT apagará o pré-scaler juntamente com o Temporizador Cão-de-Guarda. O pré-scaler não é acessível para leitura ou escrita.

A atribuição do pré-scaler está sob controle total do software (i.e. ela pode ser alterada "na hora" durante a execução do programa). Utilize as sequências de instruções apresentadas no Exemplo 6.1 para alterar a atribuição do pré-scaler do Timer0 para o WDT, a fim de evitar uma reinicialização não intencional do dispositivo.

BCF STATUS, RP0 ;Pular se já está no banco 0

CLRWDT ;Apaga WDT

CLRF TMR0 ;Apaga TMR0 e o pré-scaler

BSF STATUS, RP0 ;Muda para banco 1

MOVLW '00101111'b ;Estas 3 linhas são necessárias

MOVWF OPTION_REG ;somente se os bits PS<2:0>

CLRWDT ;forem 000 ou 001

MOVLW '00101xxx'b ;Configura o pós-scaler para

MOVWF OPTION_REG ;a proporção desejada de WDT

BCF STATUS, RP0 ;Retorna ao Banco 0

Para alterar o pré-scaler do WDT para o módulo Timer0, utilize a sequência apresentada no Exemplo 6.2. Esta precaução deve ser tomada mesmo que o WDT esteja desabilitado.

CLRWDT ;Apaga WDT e o pré-scaler

BSF STATUS, RP0

MOVLW b'xxxx0xxx’ ;Seleciona TMR0, o novo valor

;do pré-scale e fonte de clock

MOVWF OPTION_REG

BCF STATUS, RP0

TABELA 6.1: REGISTRADORES ASSOCIADOS AO TIMER0

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

01h, 101h |

TMR0 |

Registrador Módulo Timer0 |

xxxx xxxx |

uuuu uuuu |

|

0Bh, 8Bh, 10Bh, 18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

81h, 181h |

OPTION (2) |

RBPU |

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

1111 1111 |

1111 1111 |

|

85h |

TRISA |

TRISA7 |

TRISA6 |

TRISA5 |

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

1111 1111 |

1111 1111 |

Legenda:

- = posições não implementadas, lidas como "0"

u = inalterado

x = desconhecido

células sombreadas = não utilizadas para o Timer0

Nota 1: O registrador Option é referido como OPTION_REG no Software MPLAB® IDE.