Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

No modo Síncrono Mestre dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A, os dados são transmitidos de maneira half-duplex (semi-bidirecional, i.e., a transmissão e a recepção não ocorrem ao mesmo tempo). Durante a transmissão dos dados, a recepção é inibida, e vice-versa. O modo Síncrono é selecionado ativando-se o bit SYNC (TXSTA<4>). Além disso, o bit de habilitação SPEN (RCSTA<7>) é ativado para configurar os pinos I/O RB2/TX/CK e RB1/RX/DT para as linhas CK (clock) e DT (data = dados), respectivamente. O modo Mestre indica que o processador transmite o clock mestre na linha CK. O modo Mestre é selecionado ativando-se o bit CSRC (TXSTA<7>).

12.4.1 TRANSMISSÃO SÍNCRONA MESTRE DO USART

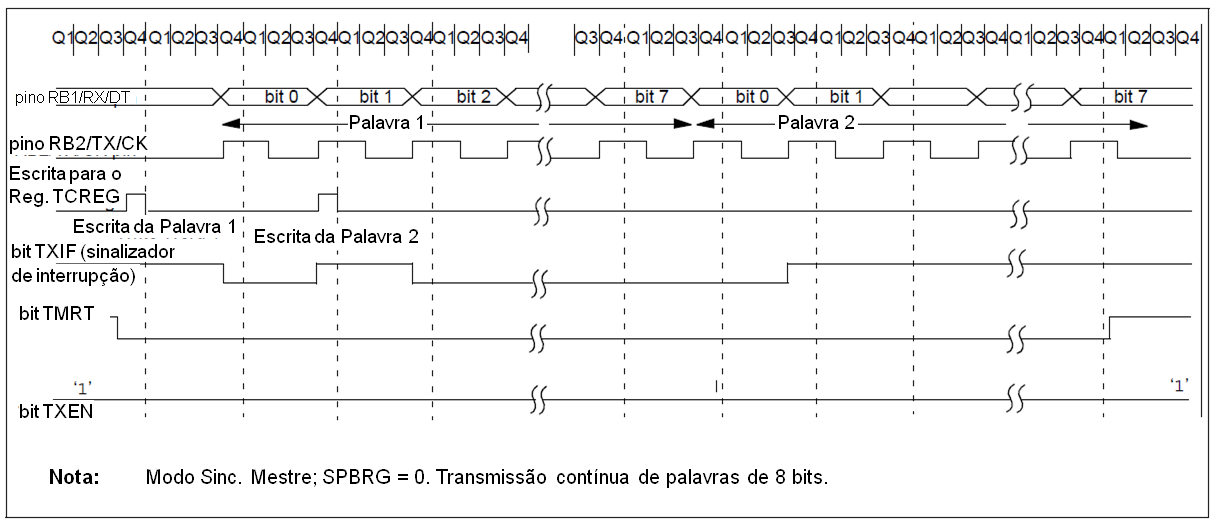

O diagrama de blocos do transmissor do USART é apresentado na Figura 12.1. O núcleo do transmissor é o Registrador de Deslocamento de Transmissão serial (TSR). O registrador de deslocamento obtém seus dados do buffer de transmissão de leitura/ escrita, TXREG. O registrador TXREG é carregado com dados pelo software. O registrador TSR não é carregado até que o último bit tenha sido transmitido do carregamento anterior. Assim que o último bit é transmitido, o TSR é carregado com novos dados provenientes do TXREG (caso estejam disponíveis). Uma vez que o registrador TXREG transfere os dados para o registrador TSR (o que ocorre em um TCICLO), o TXREG fica vazio e o bit de interrupção, TXIF (PIR<4>) é ativado. A interrupção pode ser habilitada/ desabilitada ativando-se/ apagando-se o bit de habilitação TXIE (PIE<4>). O bit de sinalização TXIF será ativado independentemente do estado do bit de habilitação TXIE e não pode ser apagado pelo software. Ele será reinicializado somente quando novos dados forem carregados para o registrador TXREG. Enquanto o bit sinalizador TXIF indica o status do registrador TXREG, um outro bit TRMT (TXSTA<1>) mostra o status do registrador TSR. O TRMT é um bit acessível somente para leitura, o qual é ativado quando o TSR está vazio. Nenhuma lógica de interrupção está relacionada a este bit, então o usuário deve eleger este bit para determinar se o registrador TSR está vazio. O TSR não é mapeado na memória de dados, então ele não está disponível para o usuário.

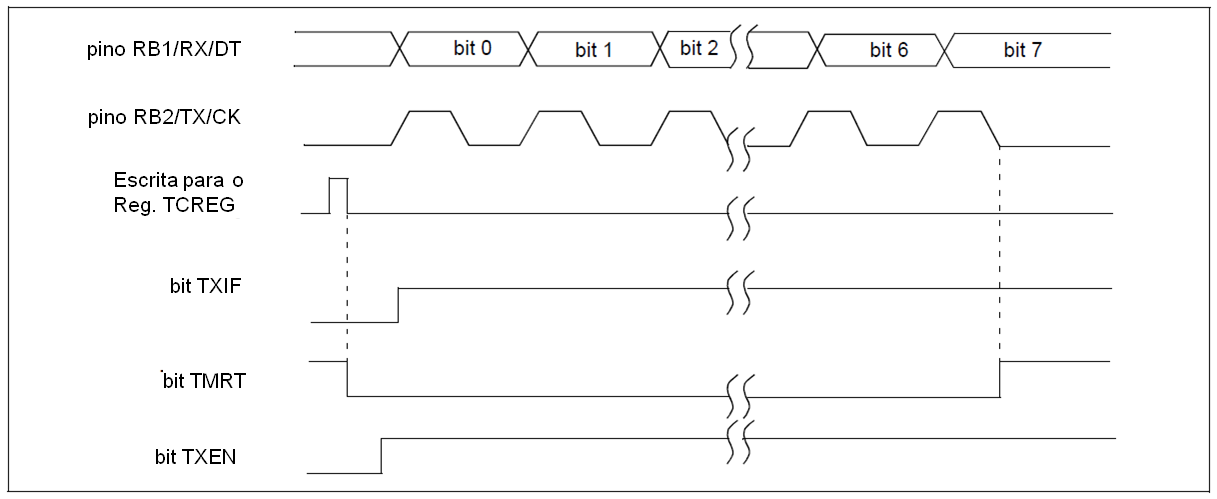

A transmissão é habilitada ativando-se o bit de habilitação TXEN (TXSTA<5>). A transmissão atual não ocorrerá até que o registrador TXREG tenha sido carregado com os dados. O primeiro bit de dados será deslocado para para a próxima borda de subida disponível no clock, na linha CK. A saída de dados é estável no entorno da borda de descida do clock síncrono (Figura 12.8). A transmissão também pode ser iniciada através do primeiro carregamento do registrador TXREG e da posterior ativação do bit TXEN (Figura 12.9). Isso é vantajoso quando taxas de transmissão lentas são selecionadas, uma vez que o BRG é mantido na Reinicialização quando os bits TXEN, CREN e SREN estiverem apagados. A ativação do bit de habilitação TXEN iniciará o BRG, criando imediatamente um clock de deslocamento. Normalmente, quando a transmissão é iniciada pela primeira vez, o registrador TSR está vazio, então uma transferência para o registrador TXREG resultará em uma transferência imediata para o TSR, resultando, por sua vez, em um TXREG vazio. Transferências back-to-back (consecutivas) são possíveis.

Ao se apagar o bit de habilitação TXEN durante a transmissão, a mesma será abortada, e o transmissor será reinicializado. Os pinos DT e CK reverterão para alta-impedância. Caso o bit CREN ou o bit SREN for ativado durante uma transmissão, a mesma será abortada, e o pino DT reverterá para o estado de alta-impedância (para uma recepção). O pino CK permanecerá uma saída se o bit CSRC for ativado (clock interno). A lógica do transmissor, entrentanto, não é reinicializada, apesar de ser desconectada dos pinos. Para reinicializar o transmissor, o usuário deve apagar o bit TXEN. Se o bit SREN for ativado (para interromper uma transmissão em curso e receber uma palavra única), então depois que a palavra única for recebida, o bit SREN será apagado e a porta serial reverterá novamente para a transmissão, desde que o bit TXEN ainda esteja ativado. A linha DT saírá imediatamente do modo de Recepção de alta impedância para transmitir e iniciar a condução. Para evitar isso, o bit TXEN deve ser apagado.

Para que a transmissão de 9 bits seja selecionada, o bit TX9 (TXSTA<6>) deve ser ativado e o nono bit deve ser escrito no TX9D (TXSTA<0>). O nono bit deve ser escrito antes da escrita dos dados de 8 bits no registrador TXREG. Isto porque uma escrita de dados no TXREG pode resultar em uma transferência imediata dos dados para o registrador TSR (se o TSR estiver vazio). Se o TSR estava vazio e o TXREG tiver sido escrito antes da escrita do "novo" TX9D, o valor "atual" do bit TX9D é carregado.

Siga estes passos ao configurar uma Transmissão Síncrona Mestre:

-

O TRISB<1> e o TRISB<2> devem ambos ser ativados para '1', a fim de configurar os pinos RB1/RX/DT e RB2/TX/CK como entradas. O drive de saída, quando requisitado, é controlado pelos circuitos periféricos.

-

Inicializar o registrador SPBRG para a taxa de transmissão apropriada (Seção 12.1 "Gerador de Taxa de Transmissão (BRG) do USART").

-

Habilitar a porta serial síncrona mestre ativando os bits SYNC, SPEN e CSRC.

-

Se interrupções forem desejadas, ativar o bit de habilitação TXIE.

-

Se a transmissão de 9 bits for desejada, ativar o bit TX9.

-

Habilitar a transmissão ativando o bit TXEN.

-

Se a transmissão de 9 bits for selecionada, o nono bit deve ser carregado para o bit TX9D.

-

Iniciar cada transmissão através do carregamento de dados para o registrador TXREG.

TABELA 12.9: REGISTRADORES ASSOCIADOS À TRANSMISSÃO SÍNCRONA MESTRE

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

18h |

RCSTA |

SPEN |

RX9 |

SREN |

CREN |

ADEN |

FERR |

OERR |

RX9D |

0000 000x |

0000 000x |

|

19h |

TXREG |

Registrador de Dados Transmitidos do USART |

0000 0000 |

0000 0000 |

|

8Ch |

PIE1 |

EEIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

0000 -000 |

|

98h |

TXSTA |

CSRC |

TX9 |

TXEN |

SYNC |

--- |

BRGH |

TRMT |

TX9D |

0000 -010 |

0000 -010 |

|

99h |

SPBRG |

Registrador Gerador de Taxa de Transmissão |

0000 0000 |

0000 0000 |

Legenda:

x = desconhecido

- = não implementado, lido como '0'

células sombreadas = não utilizadas para a transmissão síncrona mestre

12.4.2 RECEPÇÃO SÍNCRONA MESTRE DO USART

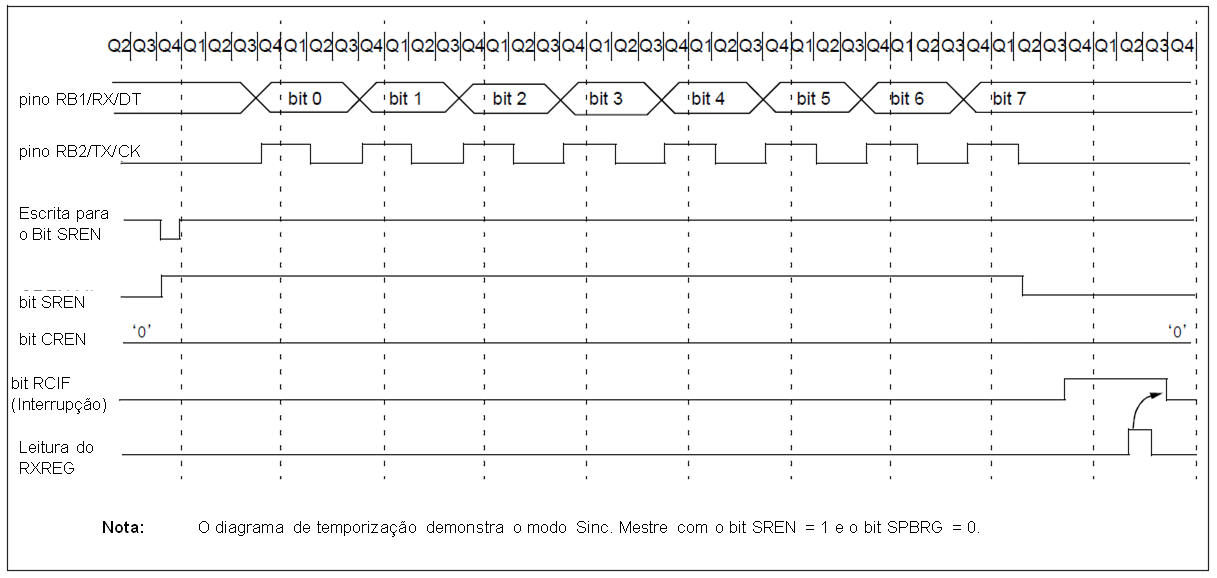

Quando o modo Assíncrono é selecionado, a recepção é habilitada ativando-se o bit de habilitação SREN (<5>) ou o bit de habilitação CREN (RCSTA<4>). Os dados são amostrados no pino RB1/RX/DT na borda de descida do clock. Se o bit de habilitação SREN estiver ativado, então somente uma palavra única é recebida. Se o bit CREN estiver ativado, a recepção é contínua até que o CREN seja apagado. Se ambos os bits estiverem ativados, então o CREN tem precedência. Depois da amostragem do último bit, os dados recebidos no Registrador de Deslocamento de Recepção (RSR) são transferidos para o registrador RCREG (se ele estiver vazio). Quando a transferência estiver completa, o bit sinalizador de interrupção RCIF (PIR1<5>) é ativado. A interrupção atual pode ser habilitada/ desabilitada ativando-se/ apagando-se o bit de habilitação RCIE (PIE<5>). O bit sinalizador RCIF é acessível somente para leitura, o qual é reinicializado pelo hardware. Neste caso, ele é reinicializado quando o registrador RCREG tiver sido lido e estiver vazio. O RCREG é um registrador de buffer duplo (i.e. é um FIFO - first in, first out = primeiro a entrar, primeiro a sair - de dois níveis). É possível que dois bytes de dados sejam recebidos e transferidos para o FIFO do RCREG, e um terceiro byte comece a ser deslocado para o registrador RSR. Na detecção do último bit do terceiro byte, se o registrador RCREG ainda estiver cheio, então o bit de erro de overrun (atropelamento) OERR (RCSTA<1>) é ativado. A palavra no RSR será perdida. O registrador RCREG pode ser lido duas vezes para recuperar os dois bytes no FIFO. O bit OERR deve ser apagado pelo software (apagando-se o bit CREN). Se o bit OERR estiver ativado, as transferências do RSR para o RCREG são inibidas, então é essencial apagar o bit OERR se ele estiver ativado. O 9º bit de recepção é armazenado temporariamente da mesma forma que os dados recebidos. A leitura do registrador RCREG carregará o bit RX9D com um novo valor, e portanto é essencial que o usuário execute a leitura do registrador RCSTA antes da leitura do RCREG, de forma a não perder as informações anteriores no RX9D.

Siga estes passos ao configurar uma Recepção Síncrona Mestre:

-

O TRISB<1> e o TRISB<2> devem ambos ser ativados para '1', a fim de configurar os pinos RB1/RX/DT e RB2/TX/CK como entradas. O drive de saída, quando requisitado, é controlado pelos circuitos periféricos.

-

Inicializar o registrador SPBRG para a taxa de transmissão apropriada. (Seção 12.1 "Gerador de Taxa de Transmissão (BRG) do USART").

-

Habilitar a porta serial assíncrona ativando os bits SYNC, SPEN e CSRC.

-

Assegure-se que os bits CREN e SREN estejam apagados.

-

Se interrupções forem desejadas, ativar o bit RCIE.

-

Se a recepção de 9 bits for desejada, ativar o bit RX9.

-

Se uma recepção única for requisitada, ative o bit SREN. Para recepção contínua, ative o bit CREN.

-

O bit sinalizador RCIF será ativado quando a recepção estiver completa, e uma interrupção será gerada se o bit de habilitação RCIE tiver sido ativado.

-

Executar a leitura do registrador RCSTA para obter o nono bit (caso esteja habilitado) e determinar se algum erro ocorreu durante a recepção.

-

Executar a leitura dos dados de 8 bits recebidos, através da leitura do registrador RCREG.

-

Caso haja ocorrido um erro OERR, eliminar o erro apagando o bit de habilitação CREN.

TABELA 12.10: REGISTRADORES ASSOCIADOS À RECEPÇÃO SÍNCRONA MESTRE

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

18h |

RCSTA |

SPEN |

RX9 |

SREN |

CREN |

ADEN |

FERR |

OERR |

RX9D |

0000 000x |

0000 000x |

|

1Ah |

RCREG |

Registrador de Dados Recebidos do USART |

0000 0000 |

0000 0000 |

|

8Ch |

PIE1 |

EPIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

-000 0000 |

-000 -000 |

|

98h |

TXSTA |

CSRC |

TX9 |

TXEN |

SYNC |

--- |

BRGH |

TRMT |

TX9D |

0000 -010 |

0000 -010 |

|

99h |

SPBRG |

Registrador Gerador de Taxa de Transmissão |

0000 0000 |

0000 0000 |

Legenda:

x = desconhecido

- = não implementado, lido como '0'

células sombreadas = não utilizadas para a recepção síncrona mestre

FIGURA 12.10: RECEPÇÃO SÍNCRONA (MODO MESTRE, SREN)