Introdução

Quando discutimos a ponte H eu chamei sua atenção para a forma como as chaves ou transistores podem ser acionados. Das várias combinações de acionamento possíveis, algumas vão causar um curto-circuito. No caso da ponte H transistorizada, se as entrada Data0 e Data1 estiverem em nível lógico alto simultaneamente, todos os transistores conduzirão corrente e haverá um curto-circuito. Logo, em hipótese alguma Data0 e Data1 podem estar em nível alto simultaneamente.

Até aqui não há novidade. A princípio bastaria evitar o estado lógico proibido e dormir tranquilo, mas infelizmente transistores não são infinitamente rápidos. São bem mais rápidos que interruptores mecânicos, mas mesmo assim levam um tempo para mudar de estado.

Tempo de atraso (delay time)

Na figura 1 temos uma versão simplificada da ponte H, com apenas uma entrada e duas saídas. Quando a entrada Data0 está em nível lógico baixo, isto é, ligada à terra, todos os transistores estão em corte. Não há corrente pelos resistores e as saídas PNP e NPN apresentam, respectivamente, 0V e 5V. Levando a entrada Data0 para o nível lógico alto, ou seja, conectando à tensão de 5V, todos os transistores conduzem e as saídas PNP e NPN passam a ter tensões de 5V e 0V respectivamente. Note que a saída PNP segue o que é aplicado em Data0 e a saída NPN apresenta o comportamento inverso.

|

|

Figura 1 |

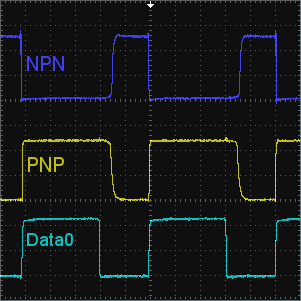

Se a tensão em Data0 for alternada rapidamente entre 0V e 5V, é esperado uma resposta compatível em ambas as saídas, ou seja, um sinal alternado idêntico a Data0 na saída PNP e um invertido na saída NPN, conforme mostrado na figura 2a. Entretanto, ao ligar as pontas de prova de um osciloscópio na entrada e saídas do circuito da figura 1, o que se apresenta é a situação mostrada na figura 2b.

|

|

|

|

Figura 2a |

Figura 2b |

Figura 2c |

Existe uma clara diferença entre o que idealizou-se na figura 2a e o que de fato foi mensurado na figura 2b. Para facilitar o entendimento, a figura 2c apresenta o mesmo gráfico de 2b de uma forma mais didática.

Nota: Na verdade, a figura 2b poderia ser omitida, apresentando apelas as figuras 2a e 2c, mas resolvi mante-la para ilustrar como um circuito real se comporta. Muitos ficam arrancando os cabelos por não conseguir leituras perfeitas em seus circuitos, mas é preciso entender que equipamentos reais são sujeitos a todo tipo de interferência. As curvas da figura 2b são aquilo que se espera de um circuito real

Percebe-se que quando Data0 passa para o nível alto, os sinais NPN e PNP respondem imediatamente. Há um pequeno atraso, mas não é visível na escala dos gráficos, que corresponde a 5µs por divisão. Já quando Data0 passa para o nível baixo, há um óbvio atraso nos sinais NPN e PNP, que só passam a mudar após 2µs. O sinal NPN atinge o nível alto após 3µs, entretanto o sinal PNP leva 3,5µs para completar a transição. Isso era esperado, já que transistores PNP são um pouco mais lentos que seus complementares. Então, para este conjunto particular de transistores, existe um atraso na resposta ao desligamento. Transistores diferentes terão tempos de resposta diferentes, por isso é sempre importante checar qual o tempo de atraso do transistor escolhido dento do circuito que se pretende construir, caso isso seja relevante.

Imagine uma situação em que as entradas Data0 e Data1 da ponte H estão, respectivamente, em nível alto e baixo e, no instante seguinte, invertem seus estados, ou seja, Data0 passa para nível baixo e Data1, para alto. Como os transistores passam a conduzir muito rapidamente mas demoram para desligar, haverá um período entre 2µs e 3µs em que todos os transistores da ponte estarão ligados!

Um curto-circuito que dure 3µs não parece grande coisa. Na verdade existem kits de controladores de motor de passo disponíveis no mercado nos quais este curto-circuito ocorre sistematicamente e parece ter sido completamente ignorado pelo projetista do circuito. O problema é que, dado tempo ao tempo, estes pulsos de alta corrente vão acabar danificando alguém. Podem queimar um regulador de tensão ou superaquecer algum transistor. Mesmo que não sejam suficientes para danificar algum componente, certamente vão gerar um ruído de linha que vai atrapalhar o funcionamento de micro-controladores, sensores e outros dispositivos lógicos.

Há algumas alternativas para evitar esta situação potencialmente danosa. Uma é usar transistores mais rápidos. Existem transistores capazes de passar da saturação para o corte em tempos muito curtos, porém eles costumam ser mais caros que os simples BD135 e BD136. Outra forma é evitar completamente a situação de uma transição simultânea de Data0 e Data1. No caso desse nosso projeto de controlador para motores de passo, basta adotar o controle monofásico ou o de meio passo. Mas há situações em que não é possível alterar a forma de controle. Nesses casos, uma solução simples é criar um atraso na ativação dos transistores que seja igual ou maior que o do desligamento. No nosso caso, um atraso de 4µs seria suficiente para garantir que tudo se desligue antes da inversão da corrente. Este atraso na ativação de um lado da ponte H após o desligamento do outro é chamado de tempo morto (dead time).

Tempo morto (dead time)

Cabe agora apresentar um circuito capaz de atrasar a ativação dos transistores sem alterar o tempo de desligamento. Isso pode ser feito com o circuito da figura 3.